По следам IFD 2010: процессорная микроархитектура Intel Sandy Bridge

Кратко о процессорах Sandy Bridge

Ядро процессора на базе микроархитектуры Sandy Bridge

Кольцевая шина в микроархитектуре Sandy Bridge

Графическое ядро в микроархитектуре Sandy Bridge

В рамках прошедшего 13-15 сентября форума IDF 2010 компания Intel впервые огласила подробности новой процессорной микроархитектуры, известной под кодовым наименованием Sandy Bridge. Собственно, процессор Sandy Bridge демонстрировался еще на прошлогоднем форуме IDF 2009, но подробности новой микроархитектуры тогда не сообщались (разве что самые общие сведения). Сразу оговоримся, что далеко не все ее подробности стали достоянием гласности и сейчас. Кое-что компания хочет оставить в секрете до официального анонса, который должен состояться в самом начале следующего года. В частности, не разглашаются подробности относительно производительности новых процессоров, модельного ряда, а также некоторых особенностей архитектуры.

Итак, давайте поближе познакомимся с новой микроархитектурой Sandy Bridge, а также с особенностями процессоров на ее базе, которые в дальнейшем мы будем называть процессорами Sandy Bridge.

Кратко о процессорах Sandy Bridge

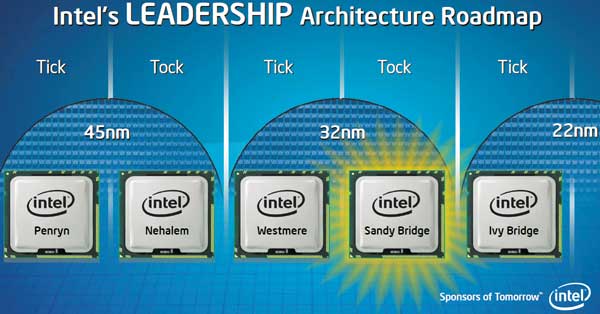

Все процессоры с кодовым наименованием Sandy Bridge первоначально будут производиться по 32-нм техпроцессу. В дальнейшем, когда состоится переход на 22-нм техпроцесс, процессоры на базе микроархитектуры Sandy Bridge получат кодовое наименование Ivy Bridge (рис. 1).

Рис. 1. Эволюция семейств процессоров Intel и процессорных микроархитектур

Процессоры Sandy Bridge, точно так же, как процессоры Westmere, образуют в настольном и мобильном сегментах три семейства: Intel Core i7, Intel Core i5 и Intel Core i3, однако логотипы этих процессоров несколько изменятся (рис. 2). Если точнее, то речь идет о втором поколении (2nd Generation) семейств Intel Core.

Рис. 2. Новые логотипы процессоров Sandy Bridge

Известно, что система маркировки процессоров полностью изменится, но на форуме IDF 2010 ничего не сообщалось относительно новой системы обозначения моделей процессоров.

По неофициальным данным, процессоры Sandy Bridge будут маркироваться четырехзначным числом, причем первая цифра — 2 — означает второе поколение семейства Intel Core. То есть будет, к примеру (опять-таки, по неофициальным данным), процессор Intel Core i7-2600 или Intel Core i5-2500. В семействах Intel Core i7 и Intel Core i5 будут процессоры как с заблокированным коэффициентом умножения, так и с разблокированным, причем последние будут обозначаться буквой K (Intel Core i7-2600K, Intel Core i5-2500K).

Основные различия между семействами Intel Core i7, Intel Core i5 и Intel Core i3 будут заключаться в размере кэша L3, количестве ядер и поддержке технологий Hyper-Threading и Turbo Boost.

Процессоры семейства Intel Core i7 будут четырехъядерными с поддержкой технологий Hyper-Threading и Turbo Boost, а размер кэша L3 составит 8 Мбайт.

Процессоры семейства Intel Core i5 будут четырехъядерными, но не будут поддерживать технологию Hyper-Threading. Ядра этих процессоров будут поддерживать технологию Turbo Boost, а размер кэша L3 составит 6 Мбайт.

Процессоры семейства Intel Core i3 будут двухъядерными с поддержкой технологии Hyper-Threading, но без поддержки технологии Turbo Boost. Размер кэша L3 в этих процессорах составит 3 Мбайт.

После оглашения неофициальных сведений перейдем к достоверным данным.

Все новые процессоры Sandy Bridge получат новый процессорный разъем LGA 1155 и, естественно, будут несовместимы с материнскими платами на базе чипсетов Intel 5-й серии. Собственно, для процессоров Sandy Bridge будут предназначены системные платы на базе нового чипсета Intel 6-й серии. Новшеством этих однокристальных чипсетов станет поддержка двух портов SATA 6 Гбит/с (SATA III), а также полноскоростных линий PCI Express 2.0 (с частотой 5 ГГц). А вот интегрированного в чипсет контроллера USB 3.0 пока не будет.

Впрочем, вернемся к процессорам Sandy Bridge. Новый процессорный разъем LGA 1155 потребует, по всей видимости, и новых кулеров, так как кулеры под разъем LGA 1156 будут несовместимы с разъемом LGA 1155. Впрочем, это лишь наша догадка, основанная на простой логике. В конце концов, должна же компания Intel както стимулировать выпуск новых моделей кулеров, дабы производители кулеров не загнулись окончательно.

Отличительной особенностью всех процессоров Sandy Bridge станет наличие в них интегрированного графического ядра нового поколения. Причем если в процессорах предыдущего поколения (Clarkdale и Arrandale) вычислительные ядра процессора и графическое ядро размещались на разных кристаллах и, более того, производились по разным техпроцессам, то в процессорах Sandy Bridge все компоненты процессора будут выпускаться по 32-нм техпроцессу и размещаться на одном кристалле.

Важно подчеркнуть, что идеологически графическое ядро процессора Sandy Bridge можно рассматривать как пятое ядро процессора (в случае четырехъядерных процессоров). Причем графическое ядро, так же как и вычислительные ядра процессора, имеет доступ к кэшу L3.

Точно так же, как процессоры предыдущего поколения Clarkdale и Arrandale, процессоры Sandy Bridge будут иметь интегрированный интерфейс PCI Express 2.0 для использования дискретных видеокарт. Причем все процессоры поддерживают 16 линий PCI Express 2.0, которые могут быть сгруппированы либо как один порт PCI Express x16, либо как два порта PCI Express x8.

Также нужно отметить, что все процессоры Sandy Bridge будут иметь интегрированный двухканальный контроллер памяти DDR3. Вариантов с трехканальным контроллером памяти пока выпускать не планируется. Связано это с тем, что модельный ряд процессоров Sandy Bridge не будет охватывать сегмент топовых настольных процессоров. Топовым настольным процессором станет новая модель шестиядерного процессора Gulftown (Intel Core i7-990X), а модельный ряд процессоров Sandy Bridge будет ориентирован на производительные, массовые и бюджетные ПК.

Еще одна особенность процессоров на базе микроархитектуры Sandy Bridge заключается в том, что вместо шины QPI (Intel QuickPath Interconnect), которая ранее использовалась для связи отдельных компонентов процессора друг с другом, теперь применяется принципиально иной интерфейс, называемый кольцевой шиной (Ring Bus), которую мы подробно рассмотрим далее.

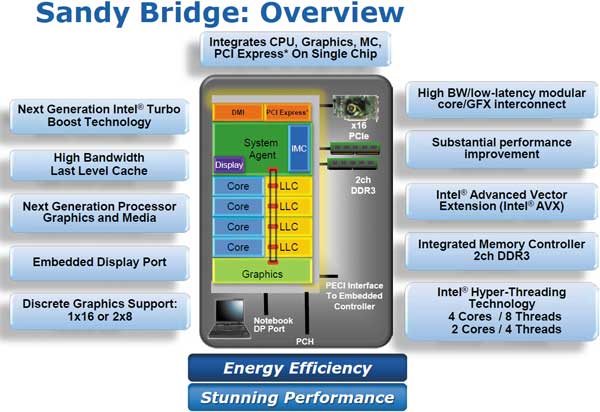

Вообще, нужно отметить, что архитектура процессора Sandy Bridge подразумевает модульную, легко масштабируемую структуру (рис. 3).

Рис. 3. Модульная структура процессора Sandy Bridge

Еще одна особенность микроархитектуры Sandy Bridge заключается в том, что в ней реализована поддержка набора инструкций Intel AVX (Intel Advanced Vector Extension).

Intel AVX представляет собой новый набор расширений для архитектуры Intel, предусматривающий 256-битные векторные вычисления с плавающей запятой на базе SIMD (Single Instruction, Multiple Data).

Intel AVX предполагает комплексное расширение архитектуры набора команд для микроархитектуры Intel 64 и обладает следующими особенностями:

- поддержка векторных данных с большей разрядностью (до 256 бит);

- эффективная схема кодирования инструкций, поддерживающая синтаксис команд с тремя и четырьмя операндами;

- гибкая среда программирования, предусматривающая различные возможности — от инструкций обработки переходов до сниженных требований к выравниванию смещений в памяти;

- новые примитивы для манипулирования данными и ускорения арифметических вычислений, включая трансляцию (broadcast), перестановку (permute), одновременное умножение и сложение (fused-multiply-add, FMA) и др.

Учитывая тот факт, что новый набор команд Intel AVX может использоваться любыми приложениями, в которых значительная доля вычислений приходится на операции SIMD, наибольший прирост производительности новая технология даст для тех из них, что преимущественно выполняют вычисления с плавающей запятой и могут быть распараллелены. В качестве примера можно назвать программы обработки звука и аудиокодеки, программы для редактирования изображений и видео, приложения для моделирования и финансового анализа, а также промышленные и инженерные приложения.

Говоря о процессорной микроархитектуре Sandy Bridge, нужно отметить, что она является развитием микроархитектуры Nehalem или Intel Core (поскольку микроархитектура Nehalem — это развитие микроархитектуры Intel Core). Различия между Nehalem и Sandy Bridge довольно существенные, однако назвать эту микроархитектуру принципиально новой, какой в свое время была микроархитектура Intel Core, всё же нельзя. Это именно модифицированная микроархитектура Nehalem.

Теперь более подробно ознакомимся с новшествами микроархитетуры Sandy Bridge и ее отличиям от Nehalem.

Ядро процессора на базе микроархитектуры Sandy Bridge

Прежде чем перейти к рассмотрению различий микроархитектур Sandy Bridge и Nehalem, напомним, что схема любого процессора подразумевает наличие нескольких конструктивных элементов: L1-кэша данных и команд, предпроцессора (Front End) и постпроцессора, называемого также блоком исполнения команд (Execution Engine).

Процесс обработки данных включает следующие этапы. Сначала инструкции и данные забираются из кэша L1 (этот этап называется выборкой). После этого выбранные из кэша инструкции декодируются в понятные для процессора машинные примитивы (микрооперации). Данная процедура называется декодированием. Далее декодированные команды поступают на исполнительные блоки процессора и выполняются, а результат записывается в память.

Процессы выборки инструкций из кэша, их декодирование и продвижение к исполнительным блокам осуществляются в предпроцессоре, а процесс выполнения команд — в постпроцессоре.

Теперь более подробно рассмотрим ядро процессора Sandy Bridge и сравним его с ядром Nehalem. При работе ядра процессора на базе микроархитектуры Nehalem или Sandy Bridge инструкции x86 выбираются из кэша инструкций L1 (Instruction Сache) размером 32 Кбайт (кэш 8-канальный). Команды загружают из кэша блоками фиксированной длины, из которых выделяются инструкции, направляемые на декодирование. Поскольку инструкции x86 имеют переменную длину, а блоки, которыми команды загружаются из кэша, — фиксированную, при декодировании команд нужно определить границы между отдельными командами.

Информация о размерах команд хранится в кэше инструкций L1 в специальных полях (по 3 бита информации на каждый байт инструкций). В принципе, эту информацию для определения границ команд можно было бы использовать в самом декодере непосредственно в процессе декодирования команд. Однако это неизбежно отразилось бы на скорости декодирования, да и нельзя было бы декодировать одновременно несколько команд. Поэтому перед декодированием производится выделение команд из выбранного блока. Данная процедура называется предварительным декодированием (PreDecode). Процедура предварительного декодирования позволяет поддерживать постоянный темп декодирования независимо от длины и структуры команд.

Процессоры с микроархитектурой Nehalem и Sandy Bridge производят выборку команд 16-байтными блоками, то есть за каждый такт из кэша загружается 16-байтный блок команд.

После операции выборки команды организуются в очередь (Instruction Queue), а затем передаются в декодер. При декодировании (Decode) команды преобразуются в машинные микрооперации фиксированной длины (обозначаются как micro-ops или uOps).

Декодер ядра процессора с микроархитектурой Sandy Bridge не претерпел изменений. Точно так же, как в микроархитектуре Nehalem, он является четырехканальным и может декодировать в каждом такте до четырех инструкций x86. Как уже отмечалось, в микроархитектурах Nehalem и Sandy Bridge за каждый такт из кэша загружается 16-байтный блок команд, из которого в процессе предварительного декодирования выделяются отдельные команды. В принципе, длина одной команды может достигать 16 байт. Однако средняя длина команд составляет 4 байта. Поэтому в среднем в каждом блоке загружаются четыре команды, которые при использовании четырехканального декодера одновременно декодируются за один такт.

Четырехканальный декодер состоит из трех простых декодеров, которые декодируют прос-тые инструкции в одну микрооперацию, и одного сложного, способного декодировать одну инструкцию в четыре микрооперации (декодер типа 4-1-1-1). Для еще более сложных инструкций, которые декодируются в более чем четыре микрооперации, сложный декодер соединен с блоком uCode Sequenser, применяемым для декодирования подобных инструкций.

Естественно, декодирование четырех инструкций за такт возможно только в том случае, если в одном 16-байтном блоке содержится не менее четырех инструкций. Однако существуют команды и длиннее 4 байт, и при загрузке нескольких таких команд в одном блоке эффективность декодирования снижается.

При декодировании инструкций в микроархитектурах Nehalem и Sandy Bridge применяются две интересные технологии — Macro-Fusion и Micro-Fusion.

Macro-Fusion — это слияние двух x86-инструкций в одну сложную микрооперацию micro-op. В предыдущих версиях процессорной микроархитектуры каждая инструкция в формате x86 декодировалась независимо от остальных. При использовании технологии Macro-Fusion некоторые пары инструкций (например, инструкция сравнения и условного перехода) при декодировании могут быть слиты в одну микрооперацию, которая в дальнейшем будет выполняться именно как одна микрооперация. Отметим, что для эффективного поддержания технологии Macro-Fusion в микроархитектурах Nehalem и Sandy Bridge применяются расширенные блоки ALU (Arithmetical Logic Unit), которые способны поддержать выполнение слитых микроопераций. Отметим также, что в случае применения технологии Macro-Fusion за каждый такт процессора может декодироваться только четыре инструкции (в четырехканальном декодере), а при использовании технологии Macro-Fusion в каждом такте может считываться пять инструкций, которые преобразуются в четыре за счет слияния и подвергаются декодированию.

Отметим, что технология Macro-Fusion использовалась и в микроархитектуре Intel Core, однако в микроархитектуре Nehalem был расширен набор x86-инструкций, для которого возможно слияние в одну микрооперацию. Кроме того, в микроархитектуре Intel Core слияние x86-инструкций не поддерживалось для 64-битного режима работы процессора, то есть технология Macro-Fusion реализовывалась только в 32-битном режиме. В архитектуре Nehalem это узкое место было устранено и операции слияния работают как в 32-, так и в 64-битном режиме процессора. В микроархитектуре Sandy Bridge набор x86-инструкций, для которых возможна операция слияния, был расширен еще больше.

Micro-Fusion — это слияние двух микроопераций (не x86-инструкций, а именно микроопераций) в одну, содержащую два элементарных действия. В дальнейшем две такие слитые микрооперации обрабатываются как одна, что позволяет уменьшить количество обрабатываемых микроопераций и тем самым увеличить общее количество инструкций, исполняемых процессором за один такт. Понятно, что операция слияния двух микроопераций возможна далеко не для всех пар микроопераций. В микроархитектуре Sandy Bridge используется точно такая же операция Micro-Fusion (для того же набора микрооперация), как и в микроархитектуре Nehalem.

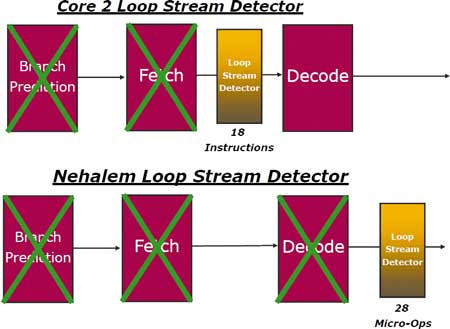

Говоря о процедуре выборки программных инструкций в микроархитектуре Nehalem, необходимо отметить наличие блока обнаружения программных циклов (Loop Stream Detector), который принимает участие в процессе выборки инструкций и позволяет избежать повторов в выполнении одних и тех же операций. Loop Stream Detector (LSD) используется и в микроархитектуре Intel Core, однако он отличается от LSD в Nehalem. Так, в архитектуре Intel Core применяется буфер LSD на 18 инструкций, причем располагается он до декодера. То есть в архитектуре Intel Core могут отслеживаться и распознаваться только циклы, содержащие не более 18 инструкций. При обнаружении программного цикла инструкции в цикле пропускают фазы выборки (Fetch) и предсказания ветвлений в программе (Branch Prediction), а сами команды генерируются и поступают в декодер из буфера LSD. С одной стороны, это позволяет снизить энергопотребление ядра процессора, а с другой — обойти фазу выборки команд. Если в цикле насчитывается более 18 инструкций, то каждый раз инструкции будут проходить все стандартные шаги.

В микроархитектуре Nehalem блок обнаружения циклов расположен не перед, а за декодером и рассчитан на 28 уже декодированных инструкций. Поскольку LSD хранит уже декодированные инструкции, они будут «пропускать» не только фазу предсказания ветвлений и выборки, как раньше, но и фазу декодирования (фактически на время выполнения программного цикла отключается предпроцессор процессора). Таким образом, в Nehalem инструкции в цикле проходят через конвейер быстрее и чаще, а энергопотребление ниже, чем в архитектуре Intel Core (рис. 4).

Рис. 4. LSD-буфер в микроархитектурах Intel Core и Nehalem

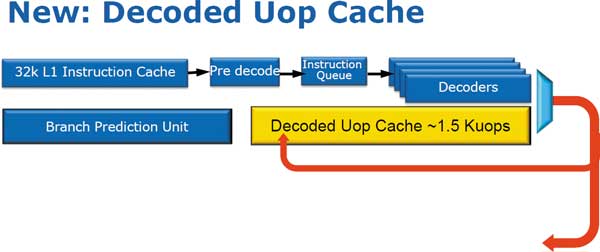

В микроархитектуре Sandy Bridge разработчики пошли еще дальше: вместе с LSD-буфером на 28 микрооперайий применили кэш декодированных микроопераций (Decoded Uop Cache) — рис. 5. В кэш поступают все декодированные микрооперации. Кэш декодированных микроопераций рассчитан приблизительно на 1500 микроопераций (видимо, речь идет о микрооперациях средней длины), что эквивалентно примерно 6-килобайтному кэшу x86-инструкций.

Рис. 5. Кэш декодированных микроопераций в микроархитектуре Sandy Bridge

Концепция кэша декодированных микроопераций заключается в том, чтобы сохранять в нем последовательности микроопераций. Кэш микроопераций работает не на уровне одной инструкции, а на уровне 32-байтного блока микроопераций. Весь кэш разделен на 32 набора, по 8 линий в каждом. На каждую линию приходится до 6 микроопераций. До 3 линий (18 микроопераций) могут быть привязаны к 32-байтному блоку. Тегирование происходит по указателю инструкции (IP). Сверка указателя предсказанной инструкции идет параллельно как в кэше инструкций, так и кэше микроопераций, и если происходит попадание, из кэша микроопераций вылавливаются линии, составляющие 32-байтный блок, и помещаются в очередь. В этом случае нет необходимости снова проводить выборку и декодирование.

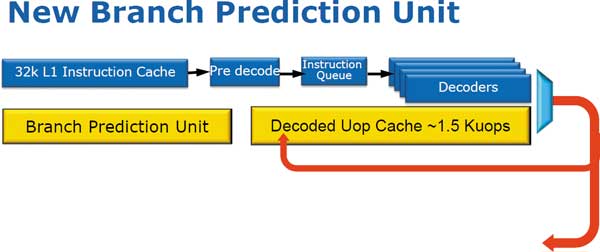

Эффективность использования кэша декодированных микроопераций во многом зависит от эффективности блока предсказания ветвлений (Branch Prediction Unit, BPU). Напомним, что блок предсказания ветвлений применяется во всех современных процессорах, причем в процессорах Sandy Bridge он существенно улучшен в сравнении с BPU в микроархитектуре Nehalem (рис. 6).

Рис. 6. Блок предсказания ветвлений (Branch Prediction Un) в микроархитектуре Sandy Bridge

Чтобы понять, почему блок предсказания ветвлений столь важен в процессоре и как он влияет на производительность, напомним, что фактически в любой болееменее сложной программе есть команды условного перехода. Команда такого условного перехода означает следующее: если некоторое условие верно, то нужно перейти к выполнению программы, начиная с одного адреса, а если нет — то с другого. С точки зрения процессора команда условного перехода является своеобразным камнем преткновения. Действительно, ведь до тех пор, пока не выяснится, верно условие перехода или нет, процессор не знает, какую часть программного кода исполнять дальше, а следовательно, вынужден простаивать. Во избежание этого как раз и используется блок предсказания ветвлений, который пытается угадать, на какой участок программного кода укажет команда условного перехода, еще до того, как она будет исполнена. На основе предсказания ветвлений производится выборка соответствующих 86-инструкций из кэша L1 или из кэша декодированных микроопераций.

Когда команда условного перехода встречается впервые, то применяется так называемое статическое предсказание. По сути, BPU прос-то угадывает, какая программная ветвь будет выполняться далее. Причем в основе статического предсказания лежит предположение, что большинство обратных ветвлений происходит в повторяющихся циклах, когда инструкция ветвления используется для определения продолжения цикла или выхода из него. Чаще всего цикл продолжается, так что процессор будет снова повторно выполнять код цикла. По этой причине статическое предсказание считает, что все обратные ветвления всегда выполняются.

По мере того как накапливается статистика результатов различных условных переходов (предыстория условных переходов), задействуется алгоритм динамического предсказания ветвлений, который как раз и основан на анализе статистики результатов условных переходов, совершенных ранее. В алгоритмах динамического предсказания ветвлений используются таблица хранения истории предсказания ветвлений (Branch History Table, BHT) и таблица хранения адресов инструкций (Branch Target Buffer, BTB). В эти таблицы записывается информация о результатах уже выполненных ветвлений. В BHT содержатся все условные переходы за несколько последних циклов. Кроме того, здесь хранятся биты, показывающие вероятность повторного выбора той же самой ветви. Биты расставляются на основании статистики предыдущих переходов. В стандартной бимодальной (2-битной) схеме существует четыре вероятности: ветвь часто выполняется (strongly taken), ветвь выполняется (taken), ветвь не выполняется (not taken) и ветвь часто не выполняется (strongly not taken).

Для того чтобы вынести решение о спекулятивном выполнении ветви, устройство должно знать точное местоположение кода в кэше L1 по направлению ветвления — назовем его целью ветвления. Цели уже выполненных ветв-лений хранятся в BTB. Когда выполняется ветвление, BPU просто берет цель ветвления из таблицы и указывает препроцессору начать выборку инструкций по этому адресу.

Понятно, что достоверность предсказания перехода зависит от размера BHT- и BTB-таблиц. Чем больше записей в этих таблицах, тем выше достоверность предсказания.

Следует отметить, что вероятность правильного предсказания ветвлений в современных процессорах очень высока (порядка 97-99%) и борьба фактически идет уже за доли процента.

Улучшений BPU в микроархитектуре Sandy Bridge несколько. Вопервых, вместо того чтобы для каждой ветви перехода использовать свою вероятность в таблице BHT, одна и та же вероятность применяется одновременно для нескольких ветвей. В результате удается оптимизировать BHT-таблицу, что сказывается на повышении достоверности предсказания переходов.

Второе улучшение BPU в микроархитектуре Sandy Bridge заключается в оптимизации BTB-таблицы. Если раньше в ВТВ для задания всех адресов переходов (branch targets) использовалось фиксированное число бит, что приводило к неоправданной трате места, то теперь количество бит, применяемых для задания адреса перехода, зависит от самого адреса. Фактически это позволяет сохранять в таблице больше адресов и тем самым повышать достоверность предсказания.

Более точных данных о размерах таблиц BHT и BTB пока нет.

Итак, об изменениях в предпроцессоре микроархитектуры Sandy Bridge (кэш декодированных микроопераций и обновленный блок предсказания ветвлений) мы рассказали. Пойдем дальше.

После процесса декодирования x86-инструкций начинается этап их исполнения. Первоначально происходит переименование и распределение дополнительных регистров процессора (блок Allocate/Rename/ Retirement), которые не определены архитектурой набора команд.

Переименование регистров позволяет добиться внеочередного исполнения команд. Идея переименования регистров заключается в следующем. В архитектуре x86 количество регистров общего назначения сравнительно невелико: доступно восемь регистров в 32-битном режиме и 16 регистров в 64-битном. Представим, что исполняемая команда дожидается загрузки значений операндов в регистр из памяти. Это долгая операция, и хорошо бы на это время позволить использовать этот регистр для другой команды, операнды которой находятся ближе (например, в кэше первого уровня). Для этого временно переименовывается «ждущий» регистр и отслеживается история переименования. А «готовому к работе» регистру присваивается стандартное имя, чтобы снабженную операндами команду исполнить прямо сейчас. При поступлении данных из памяти обращаются к истории переименования и возвращают изначальному регистру его законное имя. Иными словами, техника переименования регистров позволяет сократить простои, а ведение истории переименования применяется для нивелирования конфликтов.

На следующем этапе (буфер переупорядочения — ReOrder Buffer, ROB) происходит переупорядочение микроопераций не в порядке их поступления (Out-of-Order), чтобы впоследствии можно было реализовать их более эффективное выполнение на исполнительных блоках. Отметим, что буфер переупорядочения ReOrder Buffer и блок отставки (Retirement Unit) совмещены в едином блоке процессора, но первоначально производится переупорядочение инструкций, а блок Retirement Unit включается в работу позже, когда надо выдать исполненные инструкции в заданном программой порядке.

В микроархитектуре Nehalem в свое время был увеличен размер буфера переупорядочения в сравнении с размером буфера переупорядочения в микроархитектуре Intel Core. Так, если в Intel Core он был рассчитан на 98 микроопераций, то в Nehalem можно размещать уже 128 микроопераций.

Далее происходит распределение микроопераций по исполнительным блокам. В блоке процессора Reservation Station формирует очереди микроопераций, в результате чего микрооперации попадают на один из портов функциональных устройств (dispatch ports). Этот процесс называется диспетчеризацией (Dispatch), а сами порты выполняют функцию шлюза к функциональным устройствам.

После того как микрооперации пройдут порты диспетчеризации, они направляются в соответствующие функциональные блоки для дальнейшего выполнения.

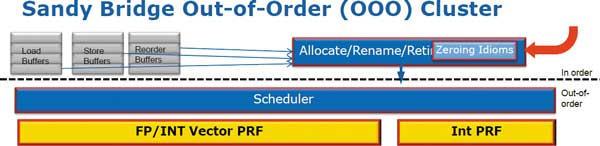

В микроархитектуре Sandy Bridge кластер Allocate/Rename/Retirement (Out-of-Order Cluster) был существенно изменен. В микроархитектурах Intel Core и Nehalem каждая микрооперация имеет копию операнда или операндов, которые ей требуются. Фактически это означает, что блоки кластера внеочередного выполнения команд должны быть достаточно большого размера, поскольку должны вмещать микрооперации вместе с необходимыми для них операндами. В архитектуре Nehalem операнды могли иметь размер 128 бит, но с введением расширения AVX размер операнда может составлять 256 бит, что требует увеличить в два раза размеры всех блоков кластера внеочередного выполнения команд.

Однако вместо этого в микроархитектуре Sandy Bridge используется физический регистровый файл (Physical Register File, PRF), в котором хранятся операнды микроопераций (рис. 7). Это дает возможность самим микрооперациям сохранять лишь указатели на операнды, но не сами операнды. С одной стороны, такой подход позволяет снизить энергопотребление процессора, поскольку перемещение по конвейеру микроопераций вместе с их операндами требует существенных затрат энергопотребления. С другой стороны, применение физического регистрового файла помогает сэкономить место на кристалле, а высвободившееся пространство использовать для увеличения размеров буферов кластера внеочередного выполнения команд (Load Buffers, Store Buffers, Reorder Buffers) — см. таблицу. В микроархитектуре Sandy Bridge физический регистровый файл для целочисленных операндов (PRF Integer) рассчитан на 160 записей, а для операндов с плавающей запятой (PRF Float Point) — на 144 записи.

Рис. 7. Использование физических регистровых файлов в микроархитектуре Sandy Bridge

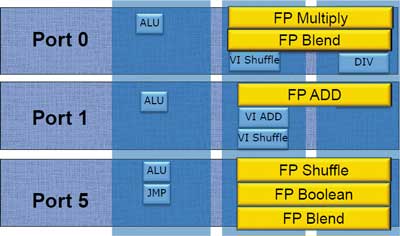

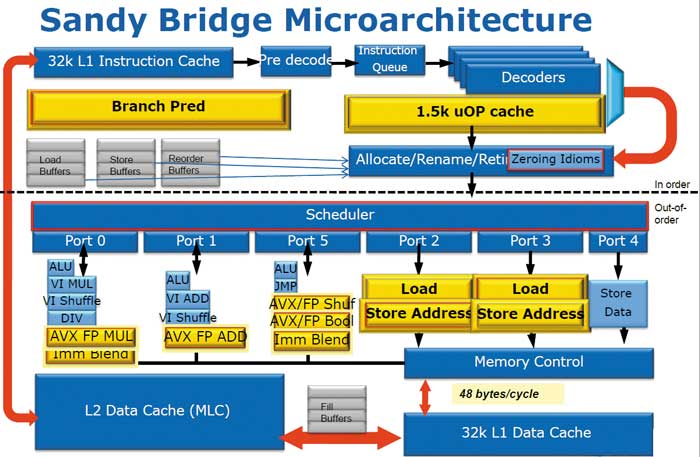

В архитектуре Sandy Bridge подверглись существенной переработке и исполнительные блоки ядра процессора. Собственно, портов функциональных устройств, как и прежде, шесть (три вычислительных и три для работы с памятью), однако их назначение, как и назначение самих исполнительных блоков, изменилось (рис. 8). Напомним, что процессор на базе микроархитектуры Nehalem способен выполнять до шести операций за один такт. При этом возможно осуществление одновременно трех вычислительных операций и трех операций с памятью.

Рис. 8. Исполнительные блоки в микроархитектуре Sandy Bridge

В архитектуре Sandy Bridge три исполнительных устройства позволяют проводить уже восемь операций с данными FP (Float Point) или две операции с 256-битными AVX-данными за такт.

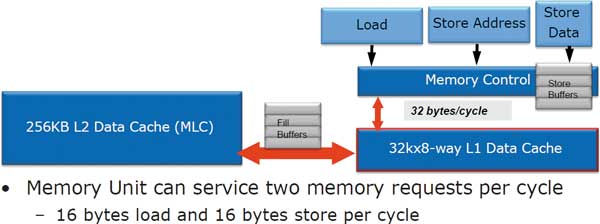

В микроархитектуре Sandy Bridge изменились не только три исполнительных устройства, но и функциональные блоки для операций с памятью. Напомним, что в микроархитектуре Nehalem было три порта для работы с памятью: Load (загрузка данных), Store address (хранение адреса), Store data (хранение данных) — рис. 9.

Рис. 9. Исполнительные блоки для работы с памятью в микроархитектуре Nehalem

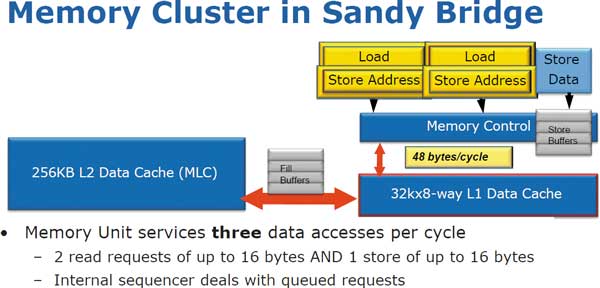

В микроархитектуре Sandy Bridge также используются три порта для работы с памятью, однако два порта стали универсальными и могут не только реализовывать загрузку данных (Load), но и сохранять адрес (Store address). Третий порт не изменился и предназначен для хранения данных (Store data) — рис. 10.

Рис. 10. Исполнительные блоки для работы с памятью в микроархитектуре Sandy Bridge

Соответственно увеличилась пропускная способность взаимодействия с кэшем данных L1. Если в микроархитектуре Nehalem за каждый такт между кэшем данных L1 и исполнительными блоками для работы с памятью могло передаваться 32 байт данных, то в микроархитектуре Sandy Bridge — уже 48 байт (два запроса на чтение по 16 байт (128 бит) и один запрос на запись до 16 байт данных).

В заключение описания ядра процессора на базе микроархитектуры Sandy Bridge сведем всё воедино. На рис. 11 показана структурная схема ядра процессора на базе микроархитектуры Sandy Bridge. Желтым цветом отмечены измененные или новые блоки в микроархитектуре Sandy Bridge, а синим — блоки, присутствующие как в микроархитектуре Nehalem, так и в Sandy Bridge.

Рис. 11. Отличия микроархитектуры Sandy Bridge от микроархитектуры Nehalem

(общие блоки отмечены синим цветом, измененные или новые блоки

в микроархитектуре Sandy Bridge — желтым)

Кольцевая шина в микроархитектуре Sandy Bridge

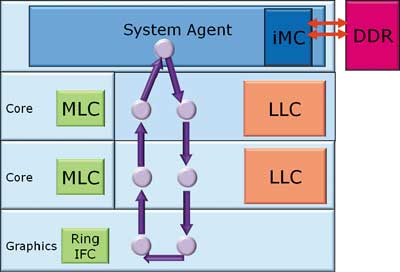

В микроархитектуре Nehalem взаимодействие между каждым кэшем L2 и разделяемым между всеми ядрами кэшем L3 осуществлялось по внутренней специальной шине процессора, насчитывающей порядка тысячи контактов, а взаимодействие между отдельными блоками процессора (контроллером памяти, графическим контроллером и т.д.) — по шине QPI. В микроархитектуре Sandy Bridge на смену шине QPI, а также шине взаимодействия L2- и L3-кэшей пришла новая кольцевая шина (Ring Bus) — рис. 12. Она позволяет организовать взаимодействие между кэшами L2 каждого ядра процессора и кэшем L3, а также реализует доступ графического ядра (GPU) и блока видеокодирования (video transcoding engine) к кэшу L3. Кроме того, по этой же кольцевой шине реализуется доступ к контроллеру памяти. Попутно отметим, что теперь компания Intel называет кэш L3 кэшем последнего уровня (Last Level Cache, LLC), а кэш L2 — промежуточным кэшем (Middle Level Cache, MLC).

Рис. 12. Кольцевая шина в микроархитектуре Sandy Bridge

Кольцевая шина объединяет в себе четыре отдельные шины: кольцевую шину данных (Data ring) разрядностью 256 бит (32 байт), кольцевую шину запросов (Request ring), шину подтверждений (Acknowledge ring) и следящую шину (Snoop ring).

Использование кольцевой шины позволило снизить латентность кэша L3. Так, в процессорах предыдущего поколения (Westmere) латентность доступа к кэшу L3 составляет 36 циклов, а в процессорах Sandy Bridge — 26-31 цикл. Кроме того, теперь L3-кэш работает на частоте ядра (в процессорах Westmere частота работы кэша L3 не соответствовала частоте ядра).

Весь L3-кэш разбит на отдельные участки, каждый из которых ассоциирован с отдельным ядром процессора. В то же время каждому ядру доступен весь кэш L3. Каждый из выделенных участков кэша L3 наделен агентом доступа к кольцевой шине. Аналогичные агенты доступа есть у кэшей L2 каждого ядра процессора, у графического ядра и у системного агента, реализующего обмен данными с контроллером памяти.

В заключение отметим, что кэш L3 в микроархитектуре Sandy Bridge остался полностью инклюзивным (включающим) по отношению к кэшам L2 (как и в микроархитектуре Nehalem).

Графическое ядро в микроархитектуре Sandy Bridge

Одно из главных нововведений в микроархитектуре Sandy Bridge — это новое графическое ядро. Как мы уже отмечали, в отличие от графического ядра в процессорах Clarkdale/Arrandale, оно расположено на одном кристалле с вычислительными ядрами процессора и, кроме того, имеет доступ через кольцевую шину к кэшу L3. Причем, как ожидается, производительность нового графического ядра будет примерно вдвое выше производительности графического ядра в процессорах Clarkdale/Arrandale. Конечно, графическое ядро в процессорах Sandy Bridge не может сравниться по производительности с дискретной графикой (кстати, поддержка DirectX 11 для нового ядра даже не заявлена), но справедливости ради отметим, что это ядро и не позиционируется как игровое решение.

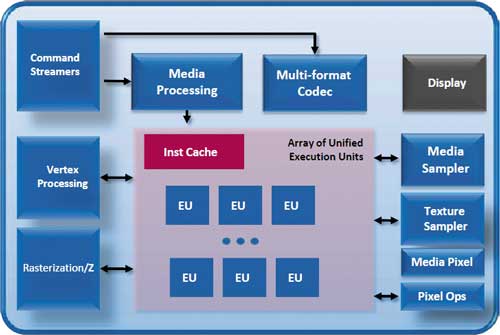

Новое графическое ядро может содержать (в зависимости от модели процессора) 6 или 12 исполнительных блоков (Execution Unit, EU), которые, впрочем, нельзя сравнивать с унифицированными шейдерными процессорами в графических процессорах NVIDIA или AMD, где их насчитывается несколько сотен (рис. 13). Данное графическое ядро ориентировано прежде всего не на 3D-игры, а на аппаратное декодирование и кодирование видео (включая HD-видео). То есть в конфигурацию графического ядра входят аппаратные декодеры. Их дополняют средства изменения разрешения (scaling), шумоподавления (denoise filtering), обнаружения и удаления чередования строк (deinterlace/film-mode detection) и фильтры улучшения детализации. Постобработка, позволяющая улучшить изображение при воспроизведении, включает функции STE (улучшение передачи телесных тонов), ACE (адаптивное повышение контраста) и TCC (общее управление цветом).

Рис. 13. Блок-схема графического ядра в микроархитектуре Sandy Bridge

Мультиформатный аппартный кодек поддерживает форматы MPEG-2, VC1 и AVC, выполняя все этапы декодирования с помощью специализированных аппаратных средств, тогда как в интегрированных графических процессорах текущего поколения эту функцию осуществляют универсальные исполнительные блоки EU.

Новый режим Intel Turbo Boost

Одной из примечательных особенностей процессоров Sandy Bridge станет поддержка нового режима Turbo Boost. Напомним, что смысл технологии Turbo Boost заключается в динамическом разгоне при определенных условиях тактовых частот ядер процессора.

Для реализации технологии Turbo Boost в процессоре предусмотрен специальный функциональный блок PCU (Power Control Unit), который отслеживает уровень загрузки ядер процессора, температуру процессора, а также отвечает за энергопитание каждого ядра и регулирование его тактовой частоты. Составной частью PCU является так называемый Power Gate (затвор), который применяется для перевода каждого ядра процессора по отдельности в режим энергопотребления C6 (фактически Power Gate отключает или подключает ядра процессора к линии питания VCC).

В процессорах Clarkdale и Arrandale режим Turbo Boost реализован следующим образом. В том случае, если какието ядра процессора оказываются незагруженными, они попросту отключаются от линии питания с использованием блока Power Gate (их энергопотребление при этом равно нулю). Соответственно тактовую частоту и напряжение питания оставшихся загруженных ядер можно динамически увеличить на несколько ступеней (по 133 МГц), но так, чтобы энергопотребление процессора не превысило его TDP. То есть фактически сэкономленное за счет отключения нескольких ядер энергопотребление используется для разгона оставшихся ядер, но так, чтобы увеличение энергопотребления в результате разгона не превышало сэкономленного энергопотребления. Более того, режим Turbo Boost реализуется и в том случае, когда изначально загружаются все ядра процессора, но при этом его энергопотребление не превышает значение TDP.

В мобильных процессорах Arrandale с интегрированным графическим ядром технология Turbo Boost распространяется не только на ядра процессора, но и на графическое ядро. То есть, в зависимости от текущей температуры и энергопотребления, разгоняться будут не только ядра процессора, но и графическое ядро. К примеру, если в какомто приложении основная нагрузка ложится на графический процессор, а ядра процессора остаются недозагруженными, то сэкономленное TDP будет использоваться для разгона графического ядра, но так, чтобы не был превышен лимит по TDP графического ядра.

Поскольку в процессорах Sandy Bridge (и в настольных, и в мобильных) графическое ядро является, по сути, таким же ядром процессора, как и вычислительные ядра, технология Turbo Boost будет распространяться как на вычислительные ядра, так и на графическое ядро. Кроме того (и в этом заключается основное новшество), в новой версии режима Turbo Boost предусмотрена возможность превышения TDP процессора при разгоне ядер на короткое время.

Дело в том, что при превышении TDP процессор перегревается не сразу, а по истечении определенного промежутка времени. Учитывая, что во многих приложениях загрузка процессора на 100% происходит скачкообразно и лишь на протяжении очень малых промежутков времени, в эти периоды тактовую частоту процессора вполне можно разгонять так, чтобы был превышен предел по TDP.

В процессорах Sandy Bridge в режиме Turbo Boost предусмотрена возможность превышения TDP на протяжении вплоть до 25 секунд (рис. 14).

Заключение

Подведем итог нашего обзора микроархитектуры Sandy Bridge. Эта новая микроархитектура представляет собой существенно переработанный вариант микроархитектуры Nehalem. Среди нововведений — использование кэша декодированных микроопераций, переработанный блок предсказания ветвлений, применение физического регистрового файла, увеличенный размер буферов кластера внеочередного выполнения команд, улучшенные исполнительные блоки процессора и блоки для работы с памятью. Кроме того, в процессорах Sandy Bridge используется кольцевая шина для доступа ядер процессора к кэшу L3 и памяти. Также процессоры Sandy Bridge получили новое, более производительное графическое ядро, которое имеет доступ к кэшу L3.

Кроме того, в процессорах Sandy Bridge реализован новый режим Turbo Boost, позволяющий выжать из процессора максимум производительности.