Новая микроархитектура Graphics Core Next и видеокарта AMD Radeon HD 7970

Архитектура унифицированных шейдерных процессоров

Понятие программных нитей и wavefront

Новая архитектура Graphics Core Next

Графический процессор с архитектурой Graphics Cores Next

Графический процессор AMD Radeon HD 7970

22 декабря прошлого года компания AMD объявила о выходе на рынок дискретной видеокарты AMD Radeon HD 7970, основанной на 28-нм графическом процессоре (GPU) на базе микроархитектуры Graphics Core Next. Эта микроархитектура является действительно революционной и отражает новый взгляд компании AMD на использование GPU.

Немного истории

Прежде чем переходить к рассмотрению видеокарты AMD Radeon HD 7970, поговорим о новом графическом процессоре на базе микроархитектуры Graphics Core Next (GCN), положенном в ее основу и известном под кодовым названием Tahiti.

Начнем с того, что архитектура графического процессора AMD существенно не корректировалась на протяжении уже четырех лет. Ее последнее революционное изменение было сделано в ATI Radeon HD серии 2000, когда произошел переход к унифицированным суперскалярным шейдерным процессорам. С тех пор никаких существенных поправок в архитектуру графических процессоров не вносилось. В частности, графический процессор AMD Radeon HD 6900 (Cayman), выпущенный в 2011 году, основан на той же архитектуре, что и процессор ATI Radeon HD 2900.

Выход процессора AMD Radeon HD 7970 ознаменовался переходом на новую архитектуру Graphics Core Next. Естественно, возникает вопрос: действительно ли старая архитектура уже изжила себя и в чем преимущество новой архитектуры? Чтобы ответить на него, давайте вспомним основные особенности архитектуры предыдущего поколения.

Общие сведения

До появления процессора ATI Radeon HD 2900 в графическом процессоре существовали специализированные конвейеры, называемые также процессорами, которые отвечали за вполне определенные действия. Так, на первом этапе графический процессор получал от центрального процессора данные об объекте, который необходимо построить. Эти данные обрабатывались в вершинном процессоре (Vertex Pipeline), который являлся частью общего конвейера обработки данных.

Обработка данных в вершинном процессоре происходила под управлением специализированной программы, называемой вершинным шейдером (Vertex Shader). На основании полученных данных вершинный процессор занимался расчетом геометрии сцены и определял положение вершин, которые при соединении образуют каркасную модель трехмерного объекта. Кроме того, в вершинном процессоре производились дополнительные операции над вершинами — преобразование и освещение (Transform & Lighting).

При помощи вершинных шейдеров вершинный процессор мог выполнять такие операции, как деформация и анимация объектов, имитация ткани, и многое другое.

На следующем этапе конвейера (Triangle) происходила сборка (Setup) трехмерной модели в полигоны. При этом вершины соединялись между собой линиями, образуя каркасную модель. При соединении вершин друг с другом образовывались полигоны (треугольники).

После сборки данные поступали в пиксельный процессор (Pixel Pipeline), который определял конечные пикселы, которые будут выведены в кадровый буфер. Пиксельный процессор в итоге своей работы выдавал конечное значение цвета пиксела и Z-значение для последующего этапа конвейера. Пиксельный процессор функционировал под управлением специальной программы, называемой пиксельным шейдером (Pixel Shader). Пиксельные шейдеры — это программы, выполняемые пиксельными процессорами во время растеризации для каждого пиксела изображения. Пиксельные шейдеры реализуют такие функции, как мультитекстурирование (наложение нескольких слоев текстуры), попиксельное освещение, создание процедурных текстур, постобработка кадра и т.д.

После обработки данных в пиксельном процессоре с использованием пиксельных шейдеров данные обрабатываются блоком растровых операций ROP (Raster Operations). На данном этапе с помощью буфера глубины (Z-буфера) определялись и отбрасывались те пикселы, которые не видны пользователю.

Кроме буфера глубины, позволяющего отсекать невидимые поверхности, при создании реалистичных трехмерных изображений необходимо учитывать, что объекты могут быть полупрозрачными. Эффект полупрозрачности создается путем объединения цвета исходного пиксела с пикселом, уже находящимся в буфере. В результате цвет точки представляет собой комбинацию цветов переднего и заднего плана. Для учета прозрачности объектов используется так называемый alpha-коэффициент прозрачности, который имеет значение от 0 до 1 (для каждого цветового пиксела).

Описанная нами классическая архитектура графического конвейера дает наглядное представление об основных этапах формирования изображения видеокартой. При этом еще раз отметим, что в описанной нами архитектуре графического конвейера используются специализированные шейдерные процессоры (вершинный, пиксельный). Однако данная схема графического конвейера не является оптимальной, поскольку подразумевает равномерное распределение нагрузки между отдельными стадиями конвейера. В реальных приложениях нагрузка на отдельные блоки графического процессора может быть различной.

Архитектура унифицированных шейдерных процессоров

Недостатки конвейерной обработки данных в графических процессорах можно было бы устранить, перейдя к архитектуре унифицированных процессоров, при которой не существует отдельных вершинных или пиксельных процессоров, а есть процессоры общего назначения, способные исполнять как вершинные, так и пиксельные шейдеры. Это позволяет избежать главного недостатка классической архитектуры — отсутствия сбалансированной нагрузки вершинных и пиксельных шейдеров.

Преимущества унифицированной шейдерной архитектуры можно объяснить следующим образом. Предположим, что в воображаемом графическом процессоре с классической архитектурой имеется четыре вершинных и восемь пиксельных процессоров. Если, к примеру, в игре используются преимущественно вершинные шейдеры (трехмерные модели с насыщенной геометрией), то может сложиться ситуация, что будут заняты все четыре вершинных процессора и только один пиксельный процессор, а оставшиеся семь пиксельных процессоров будут бездействовать. В этом случае производительность всего графического процессора будет определяться производительностью и количеством вершинных процессоров. В случае если в игре используются преимущественно пиксельные шейдеры (трехмерные модели с насыщенными пиксельными эффектами), то может возникнуть обратная ситуация, когда будет занят только один вершинный процессор и все семь пиксельных процессоров. Тогда производительность всего графического процессора будет определяться производительностью и количеством пиксельных процессоров.

Данной проблемы можно избежать, если вместо четырех вершинных и восьми пиксельных процессоров использовать 12 унифицированных шейдерных процессоров, которые могли бы выполнять как вершинные, так и пиксельные шейдеры.

Собственно, именно переход на унифицированные шейдерные процессоры был впервые реализован в процессорах ATI Radeon HD серии 2000. В использовании унифицированных шейдерных процессоров и заключалось революционное изменение архитектуры GPU.

Естественно, для унифицированных процессоров требовались новые программы обработки, то есть шейдеры (Shader Model, SM). Унифицированные процессоры на аппаратном уровне поддерживаются API Microsoft DirectX 10 и выше.

Впрочем, переход к унифицированным шейдерным процессорам в ATI Radeon HD серии 2000 был не единственным нововведением. Важно также, что унифицированные шейдерные процессоры представляли собой суперскалярные процессоры общего назначения для обработки данных с плавающей запятой. Напомним, что традиционно в процессорах задействуются два типа математики: векторная и скалярная. В случае векторной математики данные (операнды) представляются в виде n-мерных векторов, при этом над большим массивом данных производится всего одна операция. Самый простой пример — задание цвета пиксела в виде четырехмерного вектора с координатами R, G, B, A, где первые три координаты (R, G, B) задают цвет пиксела, а последняя — его прозрачность. В качестве примера векторной операции можно рассмотреть операцию сложения цвета двух пикселов. При этом одна операция осуществляется одновременно над восемью операндами (двумя четырехмерными векторами).

В скалярной математике операции осуществляются над парой чисел. Понятно, что при векторной обработке ее скорость и эффективность увеличиваются за счет того, что обработка целого набора (вектора) данных выполняется одной командой.

До появления графического процессора ATI Radeon HD серии 2000 на базе новой архитектуры унифицированных шейдерных процессоров векторная архитектура являлась в какойто мере традиционной для графических процессоров, то есть в графических процессорах предыдущего поколения применялась векторная архитектура исполнительных блоков.

В графических процессорах ATI Radeon HD серии 2000 отказались от традиционной векторной архитектуры исполнительных блоков и перешли к суперскалярной архитектуре. Так, в GPU ATI Radeon HD серии 2000 используются суперскалярные потоковые процессоры (Stream Processing Untits, SPU). В частности, в процессоре ATI Radeon HD 2900 применяются 64 SPU, которые сгруппированы в четыре блока (называемые SIMD Engine или SIMD Core) по 16 штук. Каждый SPU способен одновременно выполнять пять скалярных инструкций и состоит из пяти унифицированных суперскалярных шейдерных процессоров и одного модуля ветвлений (Branch Execution Unit). Таким образом, всего в GPU ATI Radeon HD 2900 используется 320 скалярных унифицированных шейдерных процессоров. Отметим, что блок SIMD Engine, состоящий из 16 SPU, представляет собой своеобразный мини-процессор внутри графического процессора. Таким образом, в GPU ATI Radeon HD 2900 насчитывается четыре мини-процессора SIMD Engine.

Отметим, что в процессоре ATI Radeon HD 2900 исполнительные блоки могут одновременно работать с пятью полями данных, однако сами блоки не идентичны. Дело в том, что сложные инструкции (SIN, COS, LOG) могут выполняться только одним блоком, а остальные четыре блока производят только самые простые инструкции умножения или сложения (Multiply-Add, MAD). В идеальном случае каждый из 64 SPU в процессоре ATI Radeon HD 2900 может выполнять пять MAD-операций над скалярами. В результате получается, что в процессоре ATI Radeon HD 2900 одновременно может быть реализовано 320 операций MAD.

Понятие VLIW-архитектуры

Говоря об архитектуре графических процессоров ATI Radeon HD серии 2000 и выше (вплоть до ATI Radeon HD серии 6000), немаловажно отметить, что в них использовался так называемый VLIW-дизайн (VLIW-архитектура). Собственно, понятия суперскалярности исполнительных блоков процессора и VLIW-архитектуры тесно взаимосвязаны. Действительно, под суперскалярностью исполнительных блоков понимается, что они могут параллельно выполнять несколько инструкций из одного потока. Однако для того, чтобы такое одновременное выполнение инструкций было возможно, необходимо, чтобы они были независимы друг от друга. В центральных процессорах для того, чтобы было возможно параллельное выполнение инструкций, используются специальные блоки внеочередного выполнения команд (out-of-order), которые переупорядочивают инструкции не в порядке их поступления для того, чтобы выделить из них те инструкции, которые можно выполнять параллельно, тем самым максимально загрузив исполнительные блоки процессора. Однако такое переупорядочивание инструкций «на лету» — довольно сложная техническая задача, а блоки предсказания и внеочередного выполнения команд занимают значительную часть кристалла процессора. В графических процессорах ATI Radeon HD серии 2000 стали использовать несколько иной подход, когда переупорядочение инструкций для их параллельного исполнения происходит на этапе компиляции кода. То есть на этапе компиляции выделяются независимые инструкции, которые можно выполнять параллельно, и из этих независимых инструкций формируются длинные составные конструкции, называемые VLIW-инструкциями (Very Long Instruction Word).

Отметим, что VLIW-архитектура процессора известна уже довольно давно. Она использовалась в различных центральных процессорах, в частности в несколько модифицированном виде — в процессорах Itanium.

В графических процессорах ATI Radeon HD серии 2000 каждый SPU, как уже отмечалось, наделен пятью ALU. Cоответственно в одной VLIW-инструкции может быть упаковано до пяти скалярных операций, что соответствовует пяти ALU внутри одного SPU. Именно поэтому данная архитектура получила название VLIW5.

В процессорах Radeon HD серии 6000 (кодовое наименование Cayman) также применяется VLIW-архитектура, но SPU этих процессоров содержат всего четыре исполнительных блока.

Дело в том, что внутренние исследования компании AMD показали, что в современных играх при использовании VLIW-архитектуры эффективно применяются в среднем только 3,4 исполнительных блока в SPU, то есть в среднем в одну VLIW-инструкцию удается запаковать 3,4 инструкции. А потому в процессоре Cayman количество исполнительных блоков было снижено до четырех. Соответственно в одной VLIW-инструкции может быть упаковано вплоть до четырех скалярных операций, а сама архитектура процессора стала называться VLIW4.

Для того чтобы продемонстрировать VLIW-архитектуру графического процессора, рассмотрим в качестве примера поток инструкций, переупорядоченных компилятором таким образом, чтобы все независимые инструкции были сгруппированы вместе. Предположим также, что этот поток инструкций исполняется на одном SPU с пятью ALU (рис. 1). Будем отмечать одним цветом независимые друг от друга инструкции. Последовательность таких независимых инструкций может быть упакована в одну VLIW-инструкцию, которая будет выполняться одновременно на всех исполнительных блоках SPU. В нашем примере максимальное количество независимых инструкций равно пяти, но могут быть и две независимые инструкции, и даже одна. Понятно, что в случае, когда последовательность независимых инструкций менее пяти, эффективность использования исполнительных блоков SPU снижается и для выполнения всей последовательности инструкций требуется больше тактов.

Рис. 1. Демонстрация VLIW-технологии

VLIW-технология эффективна в том случае, когда программный код содержит мало зависимостей и предсказуем. В то же время если в программе много зависимых инструкций и она плохо предсказуема, то VLIW-технология оказывается неэффективной и исполнительные блоки процессора остаются недозагруженными.

Если речь идет о рендеринге 3D-графики, то эта задача отлично распараллеливается и VLIW-архитектура графического процессора вполне себя оправдывает. Собственно, преимущество VLIW-архитектуры процессора демонстрируют видеокарты ATI, начиная с Radeon HD серии 2000 и заканчивая Radeon HD серии 6000.

Понятие программных нитей и wavefront

Одним из фундаментальных для архитектуры графических процессоров AMD является понятие wavefront. Дело в том, что все графические процессоры (и NVIDIA, и AMD) архитектурно устроены таким образом, чтобы обрабатывать одновременно множество потоков инструкций (нитей), количество которых может исчисляться тысячами. Собственно, в этом заключается главная особенность графических процессоров — возможность параллельной обработки огромного множества программных нитей. Однако эффективная обработка таких нитей возможна только в том случае, если все нити графической программы, осуществляя параллельную обработку данных, в целом движутся параллельным курсом по коду программы, причем для всех нитей в конкретный момент времени реализуется одна и та же операция, но с разными данными. Так вот, графические процессоры AMD предыдущего поколения устроены таким образом, что каждый мини-процессор (SIMD Engine) может выполнять только одну операцию (инструкцию с одним программным адресом), но с разными операндами. То есть все 16 SPU в блоке SIMD Engine процессора, к примеру, Cayman выполняют одну и ту же инструкцию. Например, это может быть инструкция сложения содержимого двух регистров: она одновременно выполняется всеми SPU блока SIMD Engine, но регистры берутся разные. Собственно, отсюда и название SIMD (Single Instruction, Multiple Data — одна инструкция, множество данных).

Напомним, что каждый SPU содержит четыре или пять (в зависимости от модели графического процессора) исполнительных блоков (ALU), что позволяет каждому SPU одновременно обрабатывать четыре или пять нитей.

При параллельной обработке программных нитей графических программ такой подход себя оправдывает и позволяет достаточно равномерно загружать все исполнительные блоки. Если же в результате ветвления в программе нити расходятся в своем пути исполнения кода, то происходит так называемая сериализация. В этом случае используются не все исполнительные блоки в SIMD Engine, поскольку нити подают на исполнение различные инструкции, а SIMD Engine может исполнять только инструкцию с одним адресом. Естественно, в этом случае производительность снижается.

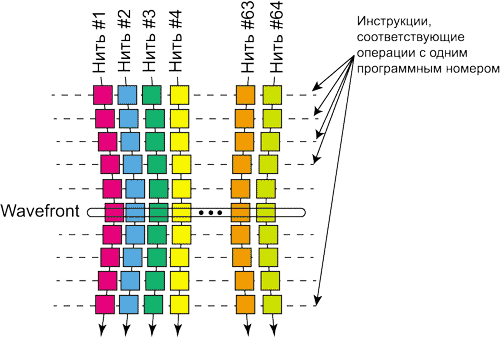

Если рассматривать параллельно расположенные нити, то перпендикулярный срез 64 нитей, соответствующих инструкции с одним программным адресом, называется wavefront (волновой фронт нитей) — рис. 2. Понятно, что в графических программах операции с одним программным адресом могут соответствовать не 64 нити, а существенно больше, то есть инструкция с одним программным адресом может порождать несколько wavefront.

Рис. 2. Понятие wavefront

Понятие wavefront очень важно, поскольку такой волновой фронт инструкций является минимальной порцией инструкций для выполнения на SIMD Engine.

Идеальной является ситуация, когда все нити выполняются параллельно (синхронно), то есть во всех нитях исполняется одна и та же инструкция. Если же происходит сериализация нитей, то, образно говоря, нужные нити подтормаживаются при выполнении до выравнивания всех нитей по номеру инструкции. При этом исполняться может даже одна нить, но это займет столько же времени, сколько и выполнение всего волнового фронта нитей. В «железе» это реализовано с помощью маскирования определенных нитей, то есть инструкции формально исполняются, но результаты их выполнения никуда не записываются и в дальнейшем не используются.

В графических процессорах AMD, начиная с Radeon HD серии 2000 и заканчивая Radeon HD серии 6000, каждый SIMD Engine обрабатывает одновременно инструкции из нескольких wavefront (по количеству ALU в SPU). В частности, в графических процессорах Radeon HD серии 6000 каждый SIMD Engine в лучшем случае может одновременно исполнять четыре wavefront, что соответствует четырем ALU в каждом SPU. В данном случае можно провести аналогию с рядами и столбцами матриц. Набор инструкций можно рассматривать как матрицу, ряды которых образуют wavefront (горизонтальный срез), а столбцы — нити инструкций. Так вот, набор из 64 ALU в каждом SIMD Engine также можно рассматривать как матрицу из 16 столбцов (по количеству SPU) и четырех рядов (по количеству ALU в каждом SPU).

Каждый такой ряд, содержащий 16 ALU, выполняет инструкции из одного wavefront, а всего в SIMD Engine одновременно может выполняться четыре wavefront. Но главное, что при этом исполняется только одна программная инструкция с разными данными.

Часто возникает ситуация, когда на SIMD Engine последовательно выполняется последовательность wavefront и некоторые из них являются зависимыми от других. Собственно, это типичная ситуация, поскольку wavefront — это лишь объединение (горизонтальный срез) из 64 отдельных нитей инструкций. А ведь инструкции в таких нитях могут зависеть друг от друга. Если в нити встречаются такие зависимые инструкции, то зависимым становится весь wavefront, поскольку, как уже отмечалось, весь набор инструкций, образующих wavefront, должен выполняться одновременно.

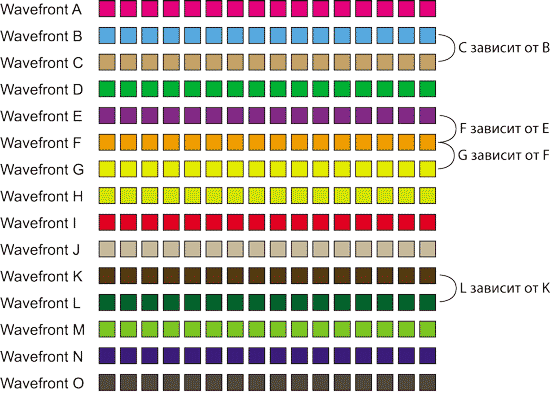

Рассмотрим в качестве упрощенного примера серию из 15 wavefront, которые будут иметь буквенные обозначения: A, B, C, D, E, F, G, H, I, J, K, L, M, N и O. Пусть wavefront С зависит от В (то есть wavefront В не может быть исполнен, пока не выполнен wavefront С). Далее, пусть wavefront F зависит от wavefront E, wavefront G — от F, а wavefront L — от K (рис. 3).

Рис. 3. Последовательность из 15 wavefront с зависимостями

В первом такте SIMD Engine сможет исполнять одновременно инструкции из wavefront A и B, поскольку они не зависят друг от друга. При этом из четырех ALU в каждом SPU будут задействованы только два, поскольку wavefront C не может быть выполнен, пока не выполнен wavefront B (рис. 4).

Рис. 4. Выполнение последовательности 15 wavefront с зависимостями

на SIMD Engine с архитектурой VLIW4

Во втором такте в SIMD Engine могут выполняться одновременно wavefront C, D и E. Соответственно в каждом SPU будут задействоваться три ALU.

В третьем такте в SIMD Engine может исполняться только wavefront F, поскольку, во-первых, он должен быть выполнен после wavefront E, а во-вторых, wavefront G должен быть выполнен после wavefront F. Соответственно в каждом SPU будет задействоваться только один ALU.

В четвертом такте могут быть выполнены wavefront G, H, I и J (все они не зависят друг от друга). Таким образом, в каждом SPU будут задействованы все четыре ALU.

В следующем такте выполняется только один wavefront K, поскольку следующий за ним wavefront L зависит от wavefront K и не может исполняться одновременно с ним.

Ну и в последнем, шестом такте могут одновременно выполняться wavefront L, M, N и O.

Таким образом, для выполнения всех 15 wavefront c учетом зависимостей потребовалось шесть тактов. Понятно, что если бы зависимости отсутствовали, то для выполнения всех wavefront потребовалось бы четыре такта.

Новая архитектура Graphics Core Next

Мы напомнили особенности суперскалярной VLIW-архитектуры графических процессоров AMD. Однако VLIW-архитектура — это уже история, поскольку в новой архитектуре Graphics Core Next графических процессоров AMD она больше не применяется. Как мы увидим в дальнейшем, новая микроархитектура GCN основана на векторном SIMD-дизайне.

Однако прежде давайте выясним, почему компания AMD отказалась от суперскалярной VLIW-архитектуры и решилась на столь резкий поворот. Ответ довольно прост: тренд современности заключается в том, что графические процессоры видеокарт всё больше используются не только для игр, но и для других вычислений (расчетов общего назначения). Если бы речь шла исключительно об играх, где графические процессоры рассчитывают только 3D-рендеринг, то, возможно, VLIW-архитектура могла бы послужить еще. Однако сегодня GPU постепенно трансформируются в GPGPU (General Purpose GPU), которые можно применять для любых массивных параллельных вычислений. Лоббирует эту тему прежде всего компания NVIDIA со своей технологией CUDA, и надо отметить, что она добилась немалых успехов. Естественно, AMD тоже не желает оставаться в стороне и прилагает все усилия, чтобы превратить свои GPU в GPGPU. Однако суперскалярная VLIW-архитектура графического процессора плохо подходит для вычислений типа General Purpose, поскольку они менее предсказуемы, чем 3D-рендеринг, и в этих условиях не удается эффективно загружать вычислительные блоки SPU. То есть VLIW-архитектура прекрасно подходит для GPU, но очень плохо оптимизирована для GPGPU.

Собственно, новая архитектура GCN — это архитектура первого процессора GPGPU от компании AMD. Насколько такая универсализация графических процессоров оправдана и востребована — вопрос отдельный. Отметим лишь, что сегодня вычисления на GPU активно используются в сегменте высокопроизводительных вычислений (HPC) на суперкомпьютерах. Но этот сегмент рынка уже давно «застолбила» за собой компания NVIDIA со своим CUDA-процессором TESLA. А вот компанию AMD на этом рынке, похоже, никто не ждет.

Что же касается традиционных пользовательских приложений, то программ, оптимизированных под расчеты на GPU, пока ничтожно мало, да и необходимость такой оптимизации вообще сомнительна. Помните, были времена, когда функцию графического процессора (GPU) выполнял центральный процессор (CPU)? Так вот, теперь ситуация повторяется, но с точностью до наоборот: графический процессор заменяет собой центральный. На наш взгляд, подменять центральный процессор графическим — не самый лучший вариант. Уж лучше создать для массивных параллельных вычислений специализированный сопроцессор для центрального процессора, а не универсальную архитектуру графического процессора под задачи 3D-рендеринга и параллельных вычислений общего назначения. Ведь, как известно, любое универсальное устройство всегда хуже специализированного. Вопрос в данном случае стоит так: если бы компания AMD, как и прежде, использовала VLIW-дизайн графического процессора с незначительными изменениями архитектуры (увеличение числа SPU и т.д.) за счет перехода на новый, 28-нм техпроцесс, то был ли бы получившийся у нее гипотетический графический процессор производительнее в играх, чем процессор AMD Radeon HD 7970? Понятно, что ответ на него мы не узнаем никогда, но есть все основания полагать, что гипотетический графический процессор был бы более производительным в играх. Однако компания AMD выбрала иной путь и создала GPGPU-процессор, который подходит и для игр, и для параллельных вычислений общего назначения.

Итак, теперь самое время ознакомиться с особенностями архитектуры Graphics Core Next, которая пришла на смену суперскалярной VLIW-архитектуре.

Блок Compute Unit

Основой графического процессора на базе архитектуры Graphics Cores Next (GCN) является Compute Unit, который представляет собой своеобразный «строительный кирпичик» и является аналогом SIMD Engine в графических процессорах предыдущего поколения.

Как уже отмечалось, в процессоре Cayman (Radeon HD 6950/6970/6990) c архитектурой VLIW4 блок SIMD Engine составляют 16 суперскалярных SPU, в каждом из которых содержится четыре ALU. То есть всего в SIMD Engine имеется 64 ALU.

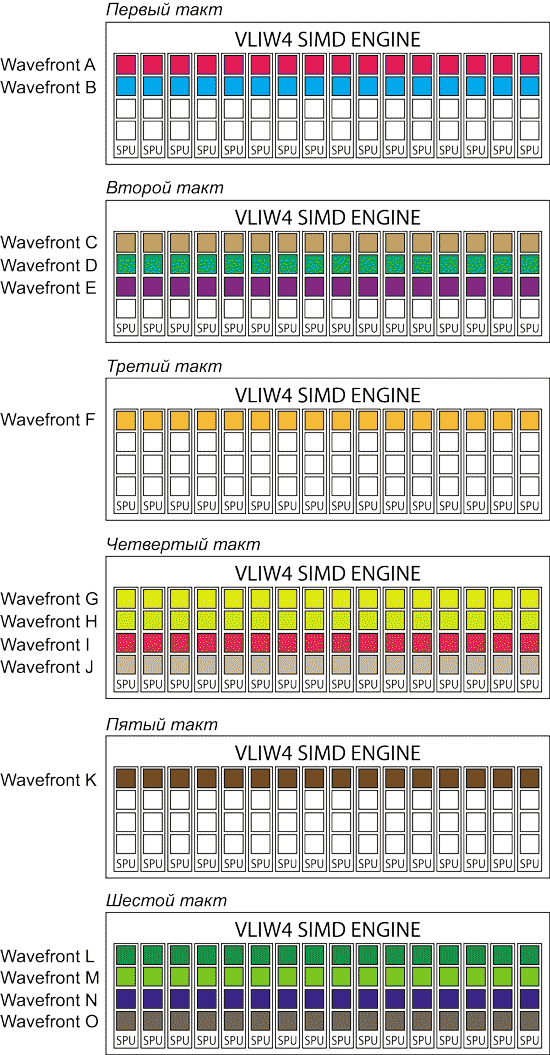

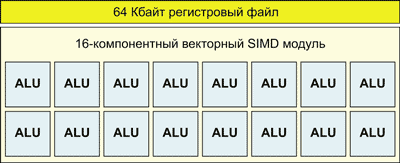

Блок Compute Unit (рис. 5) устроен совершенно по-иному. В нем тоже 64 ALU, но они разделены на четыре отдельных векторных SIMD-модуля (Vector Unit, VU) по 16 ALU в каждом (рис. 6). Казалось бы, какая разница: 16 блоков (SPU) по четыре ALU в каждом (организация 16x4) или четыре блока VU по 16 ALU в каждом (организация 4x16)?

Рис. 5. Структура блока Compute Unit

в архитектуре Graphics Cores Next

Рис. 6. Структура векторного SIMD-модуля

в архитектуре Graphics Cores Next

Если в процессоре Cayman все 16 SPU образовывали один блок SIMD Engine, который мог исполнять только одну программную инструкцию, но с разными операндами, то в блоке Compute Unit имеются четыре отдельных векторных SIMD-модуля. Как несложно догадаться, эти четыре SIMD-модуля могут одновременно выполнять четыре различные программные операции.

Собственно, ключевая разница заключается в том, что эти архитектуры обеспечивают разный тип параллелизма. Организация 16x4 позволяет реализовать параллелизм на уровне инструкций (Instruction Level Parallelism, ILP), а организация 4x16 — на уровне потоков (Thread Level Parallelism, TLP). Дело в том, что в блоке CU может динамически распределяться нагрузка между векторными SIMD-модулями, для чего в каждом CU имеется аппаратный планировщик (Sheduler). То есть если в процессорах предыдущего поколения с архитектурой VLIW выполнялось статическое планирование, то в архитектуре Compute Unit — динамическое.

Нагрузка для параллельного исполнения поступает в каждый векторный SIMD-модуль в виде wavefront (массива из 64 инструкций), который выполняется за четыре цикла. И хотя одновременно в работе могут быть только четыре wavefront, еще несколько находятся у Compute Unit в прямом доступе, за счет чего планировщик получает возможность маневра. В ситуации, когда зависимость в коде мешает векторному SIMD-модулю работать на полную мощность, этот модуль переключается на выполнение другого wavefront. Каждый векторный SIMD-модуль может выполнять один из десяти wavefront и динамически переключаться между ними. Всего же CU может распределять по векторным SIMD-модулям сорок wavefront.

Отметим, что, несмотря на наличие аппаратного планировщика в каждом CU и возможность динамического изменения загрузки векторных SIMD-модулей, архитектура Graphics Cores Next не является архитектурой внеочередного выполнения команд (Out-Of-Order). В рамках одного wavefront все команды исполняются последовательно, однако имеется возможность переключаться между отдельными wavefront.

Кроме упомянутых векторных SIMD-модулей, в каждом CU есть отдельный скалярный модуль, который предназначен для разовых операций, не укладывающихся в wavefront (что избавляет SIMD-модули от неэффективного использования), а также для контроля исполнения программы: условных ветвлений, переходов и прочих событий. Скалярный модуль выполняет одну операцию за цикл.

При рассмотрении архитектуры VLIW4 мы разбирали упрощенный пример выполнения серии из 15 wavefront (A, B, C, D, E, F, G, H, I, J, K, L, M, N, O), которые имели зависимости. Напомним, что wavefront С зависел от В, wavefront F — от wavefront E; wavefront G — от F, wavefront L — от K. Для выполнения такой последовательности на SIMD Engine процессора с архитектурой VLIW4 потребовалось шесть тактов.

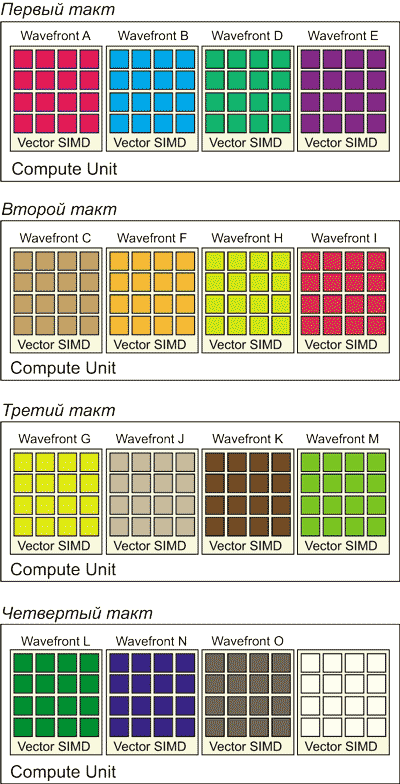

Теперь давайте посмотрим, сколько тактов нужно для выполнения той же последовательности wavefront на CU процессора с архитектурой Graphics Cores Next (рис. 7).

Рис. 7. Выполнение последовательности 15 wavefront

с зависимостями на CU

В первом такте в каждый из четырех VU загружаются и выполняются wavefront A, B, D и E. Однако поскольку wavefront С зависит от wavefront B, он не может выполняться одновременно с ним и планировщик CU динамически переключает VU на выполнение следующих wavefront (D и E).

На втором такте выполняется отложенный wavefront С и независящие друг от друга wavefront F, H и I. А вот исполнение wavefront G откладывается, поскольку он зависит от wavefront F.

В третьем такте выполняется отложенный wavefront G, а также wavefront J, K и M, а исполнение wavefront L, который зависит от К, откладывается.

В последнем, четвертом такте происходит выполнение отложенного wavefront L и следующих по порядку, не зависящих друг от друга wavefront N и O.

Как видите, в нашем примере для выполнения всей последовательности из 15 wavefront потребовалось всего четыре такта, а не шесть, как в случае с SIMD Engine. Таким образом, при выполнении последовательности wavefront с зависимостями преимущество архитектуры Graphics Cores Next налицо.

Итак, Compute Unit в архитектуре Graphics Cores Next является своеобразным мини-процессором графического процессора.

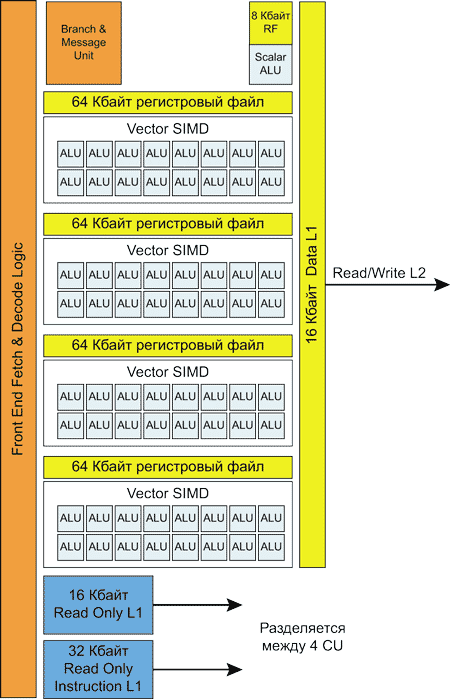

Кроме четырех векторных SIMD-модулей по 16 ALU в каждом, CU содержит, как уже отмечалось, отдельный скалярный модуль, а также отдельный кэш данных L1 объемом 16 Кбайт, разделяемый между несколькими CU кэш L1 инструкций размером 16 Кбайт и разделяемый между несколькими CU кэш данных размером 32 Кбайт.

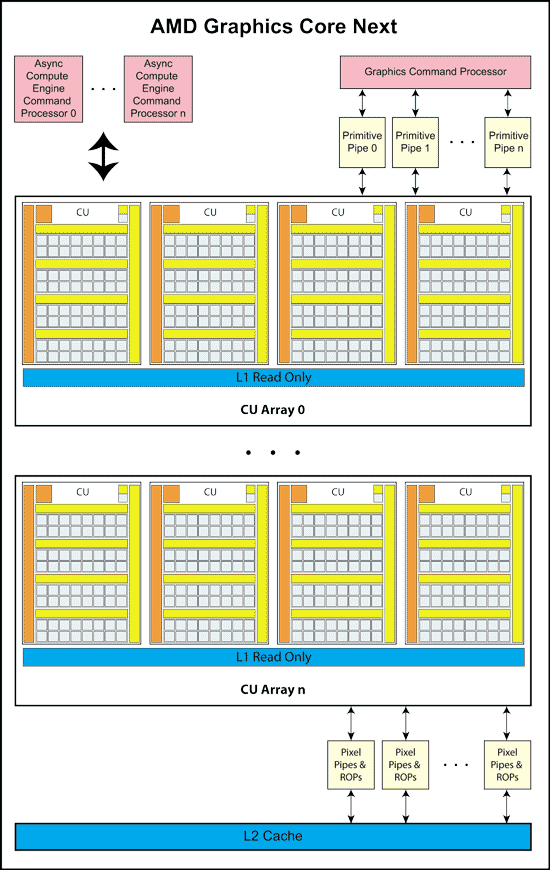

Графический процессор с архитектурой Graphics Cores Next

Мы подробно рассмотрели основной блок графического процессора с архитектурой Graphics Cores Next, называемый Compute Unit. Понятно, что сам по себе CU еще не является графическим процессором, но представляет собой структурный элемент для создания такового. Собственно, графический процессор включает несколько СU, причем их число должно быть кратно 4 (рис. 8). То есть в графическом процессоре все CU сгруппированы по четыре штуки в своеобразные области и на каждую из них приходится L1 кэш инструкций размером 16 Кбайт и L1 кэш данных размером 32 Кбайт.

Рис. 8. Структурная схема ядра Graphics Cores Next

Что касается остальных блоков, традиционных для графических процессоров AMD, то они не претерпели кардинальных изменений в новой архитектуре. Блок тесселяции (Tesselator) обновился до девятой версии в сравнении с процессором Cayman, обновлен и блок Geometry Engine.

Кроме того, если раньше блок Graphics Engine состоял из отдельных блоков для растеризации, тесселяции и т.д., то теперь в нем может быть произвольное количество конвейеров для обработки пикселов и геометрических примитивов. Такой дизайн, очевидно, позволяет просто масштабировать графический процессор.

В ядре Graphics Cores Next появились блоки распределения команд под названием Asynchronous Compute Engine (ACU) (в процессоре Cayman их не было), которые работают совершенно независимо друг от друга и от графического командного процессора (GFX Command Processor). Причем число этих ACU масштабируется и их количество может быть различным в разных графических процессорах. По всей видимости, ACU предназначены как раз для вычислительных задач общего назначения и будут доступны программистам через OpenCL.

Следующее нововведение заключается в том, что ядро GCN и центральный процессор компьютера (CPU) могут иметь общее адресное пространство. В таком случае все инструкции, которые попадают на исполнение в GPU, указывают на адреса в пространстве x86-64, а графический процессор уже самостоятельно перекодирует их в адреса локальной видеопамяти при помощи специального модуля. В результате GPU получает прямой доступ к системной памяти. Кроме того, ядро GCN наделили рядом функций для поддержки языков высокого уровня: виртуальными функциями, указателями, рекурсией и т.д. Это позволит программистам писать универсальный код, пригодный для исполнения на CPU или GPU.

Новые графические процессоры на базе архитектуры GCN полностью совместимы с API OpenCL 1.2, DirectCompute 11.1 (и DirectX 11.1 как таковой) и C++ AMP. Появились специальные инструкции, полезные для производства мультимедийного контента.

Кроме того, изменился интегрированный видеопроцессор Unified Video Decoder (UVD). Теперь он поддерживает кодирование видео еще и по стандарту H.264, а декодер видео — несколько дополнительных форматов: MVC, MPEG-4/DivX и Dual Stream HD + HD.

Также стоит отметить, что графические процессоры AMD нового поколения поддерживают новую шину PCI Express 3.0, пропускная способность которой вдвое больше по сравнению с шиной PCI Express 2.0. Возможно, сегодня увеличение пропускной способности шины и не отразится на производительности видеокарт в играх, тем не менее это хороший задел на будущее.

Большие нововведения в графических процессорах AMD нового поколения касаются энергосбережения. В частности, на графических процессорах впервые реализована технология динамического разгона тактовой частоты PowerTune, как на центральных процессорах. Дело в том, что в обычных играх далеко не всегда достигается (практически никогда) пиковое энергопотребление графического процессора, поэтому тактовую частоту можно увеличить. Для этого специальный блок GPU в реальном времени с интервалами в единицы миллисекунд рассчитывает энергопотребление, и если есть возможность, то тактовая частота GPU увеличивается.

Кроме того, ядро GCN может полностью отключиться, если нагрузка на него в течение длительного времени равна нулю.

Графический процессор AMD Radeon HD 7970

После детального знакомства с новой архитектурой Graphics Core Next давайте рассмотрим ее первое воплощение — графический процессор AMD Radeon HD 7970 и видеокарту на его основе.

Процессор AMD Radeon HD 7970 изготовлен по 28-нм техпроцессу и сегодня является самым производительным графическим процессором в семействе AMD. Этот графический процессор носит кодовое название Tahiti XT, и в нем содержится более 4 млрд (4 312 711 870) транзисторов.

Процессор Tahiti XT имеет 2048 потоковых процессоров, то есть в нем 32 ядра CU, в каждом из которых 64 потоковых процессора (вычислительных модулей ALU). Соответственно в каждом из них восемь блоков (CU Array) по четыре CU. Кроме того, чип Tahiti XT наделен 128 текстурными модулями (TMU) и 32 блоками растеризации (ROP).

Референсная графическая карта AMD Radeon HD 7970 имеет 3 Гбайт памяти GDDR5 с 384-битным интерфейсом, функционирующей на частоте 1375 МГц, а частота графического ядра составляет 925 МГц (см. таблицу).

Также стоит отметить наличие двух микросхем BIOS с возможностью переключения между ними, что позволяет прописать разгонный профиль в одну из BIOS.

Референсная видеокарта AMD Radeon HD 7970 имеет интерфейс PCI Express 3.0, а для подключения мониторов предназначены разъемы DVI и HDMI, а также два разъема Mini DisplayPort.

HDMI-выход соответствует стандарту 1.4а, поэтому может передавать двойной сигнал на 3D-телевизор с частотой 24 кадра на каждый канал. Специально для игр есть поддержка 3 ГГц HDMI с частотой 60 Гц на канал. Кроме того, стандарты DisplayPort 1.2 HBR 2 и 3 GHz HDMI пригодятся для подключения грядущих дисплеев с разрешением 4096x2160.

Отметим, что новые видеокарты AMD Radeon HD 7970 поддерживают стандарт DisplayPort 1.2, а значит, и технологию Multi-Stream. С ее помощью можно подключать к одному выходу три дисплея по цепочке или через специальный хаб. Причем на выходе хаба может быть не только DisplayPort, но и интерфейсы HDMI, DVI и VGA. Компания AMD обещает, что такие хабы появятся в продаже летом теущего года.

Также видеокарта на процессоре AMD Radeon HD 7970 поддерживает новую версию технологии AMD Eyefinity 2.0, которая представляет собой сочетание технологий AMD Eyefinity Technology и AMD HD3D Technology и позволяет видеокарте воспроизводить большое изображение либо на пяти выстроенных в ряд мониторах с ландшафтной или портретной ориентацией экранов, либо на шести мониторах с ландшафтной ориентацией экранов, составленных по три в два ряда. Также можно выводить единое трехмерное изображение сразу на три 3D-дисплея с интерфейсом DisplayPort и частотой обновления 120 Гц. Более того, для каждого монитора теперь предусмотрен свой звуковой канал, что позволяет, например, устраивать видеоконференции с несколькими собеседниками одновременно или играть на одной группе мониторов и параллельно просматривать фильм на другом. Максимальное разрешение составного экрана — 15x15 тыс. пикселов.

Кроме того, существенной модернизации подверглась референсная система охлаждения (в сравнении с тактовой на видеокарте AMD Radeon HD 6970). В частности, вентилятор стал шире и имеет лопасти новой формы, благодаря чему увеличился создаваемый им воздушный поток без значительного изменения уровня шума. Испарительная камера в основании кулера тоже была усовершенствована.

В заключение отметим, что рекомендованная цена видеокарты AMD Radeon HD 7970 составляет 500 долл.