Современная память DDR2

появлением на массовом рынке новых платформ все большую популярность приобретает память DDR2, которая постепенно начинает вытеснять память DDR. Первоначально существовала только память DDR2-400, на смену которой довольно быстро пришла память DDR2-533. А сейчас уже можно встретить память DDR2-667, DDR2-675, DDR2-750, DDR2-800, DDR2-900, DDR2-1000 и даже DDR2-1066. При этом отметим, что стандартизированной памятью в настоящее время является DDR2-533 и DDR2-667. В скором будущем будет также стандартизирована память DDR2-800, в связи с чем многие материнские платы уже поддерживают этот тип памяти. Остальные же типы памяти не стандартизированы, и не факт, что материнская плата способна поддержать эту память на заявленной тактовой частоте. Возникает вопрос: почему же производители памяти, соревнуясь друг с другом, стараются выпускать все более скоростную память? Ответ довольно прост — это маркетинговый ход. Ведь, по мнению рядового покупателя, чем выше тактовая частота, тем лучше. Но так ли это на самом деле и действительно ли производительность памяти целиком и полностью определяется ее тактовой частотой? Действительно ли сегодня востребована скоростная память типа DDR2-1000 или же это не более чем соревнование между производителями памяти?

появлением на массовом рынке новых платформ все большую популярность приобретает память DDR2, которая постепенно начинает вытеснять память DDR. Первоначально существовала только память DDR2-400, на смену которой довольно быстро пришла память DDR2-533. А сейчас уже можно встретить память DDR2-667, DDR2-675, DDR2-750, DDR2-800, DDR2-900, DDR2-1000 и даже DDR2-1066. При этом отметим, что стандартизированной памятью в настоящее время является DDR2-533 и DDR2-667. В скором будущем будет также стандартизирована память DDR2-800, в связи с чем многие материнские платы уже поддерживают этот тип памяти. Остальные же типы памяти не стандартизированы, и не факт, что материнская плата способна поддержать эту память на заявленной тактовой частоте. Возникает вопрос: почему же производители памяти, соревнуясь друг с другом, стараются выпускать все более скоростную память? Ответ довольно прост — это маркетинговый ход. Ведь, по мнению рядового покупателя, чем выше тактовая частота, тем лучше. Но так ли это на самом деле и действительно ли производительность памяти целиком и полностью определяется ее тактовой частотой? Действительно ли сегодня востребована скоростная память типа DDR2-1000 или же это не более чем соревнование между производителями памяти?

Оказывается, что тактовая частота — далеко не единственная и даже не самая главная характеристика памяти, определяющая ее производительность. Куда более важной характеристикой является латентность памяти (тайминги памяти), и в этом смысле память DDR2-800 с большой латентностью будет менее производительной, чем память DDR2-667 с низкой латентностью.

Впрочем, чтобы разобраться во всех этих нюансах и выяснить, что такое латентность и почему эта характеристика более важна, чем тактовая частота, нам надлежит сначала понять, как работает оперативная память.

Что такое оперативная память

перативная память (или RAM-память —Random Access Memory) — это память с произвольным доступом.

перативная память (или RAM-память —Random Access Memory) — это память с произвольным доступом.

Поскольку элементарной единицей информации является бит, оперативную память можно рассматривать как некий набор элементарных ячеек, каждая из которых способна хранить один информационный бит.

Элементарная ячейка оперативной памяти представляет собой конденсатор, способный в течение короткого промежутка времени сохранять электрический заряд, наличие которого можно ассоциировать с информационным битом. Проще говоря, при записи логической единицы в ячейку памяти конденсатор заряжается, при записи нуля — разряжается. При считывании данных конденсатор разряжается через схему считывания, и если заряд конденсатора был ненулевым, то на выходе схемы считывания устанавливается единичное значение.

Поскольку элементарной единицей информации для современных компьютеров является байт (восемь бит), то для простоты можно считать, что элементарная ячейка памяти, которая может адресоваться, хранит не бит, а байт информации. Таким образом, доступ в памяти производится не побитно, а побайтно.

Микросхемы памяти организованы в виде матрицы, напоминающий лист бумаги в клетку, причем пересечение столбца и строки матрицы задает одну из элементарных ячеек. Кроме того, современные чипы памяти имеют несколько банков, каждый из которых можно рассматривать как отдельную матрицу со своими столбцами и строками.

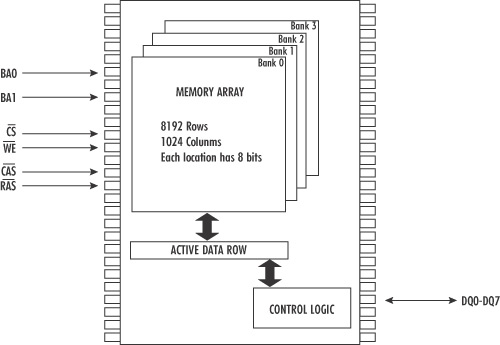

На рис. 1 показана упрощенная схема чипа памяти, в котором имеется четыре банка, каждый из которых содержит 8192 строки и 1024 столбца. Таким образом, емкость каждого банка — 8192x1024 = 8192 Кбайт = 8 Мбайт. Учитывая, что в чипе имеется четыре банка, получается, что полная емкость чипа составляет 32 Мбайт.

Рис. 1. Упрощенная схема чипа памяти

При обращении к той или иной ячейке памяти следует задать адрес нужной строки и столбца.

Для того чтобы получить доступ к ячейке памяти для записи или считывания информации, необходимо задать адрес этой ячейки. С учетом того, что в модуле памяти используется несколько чипов памяти, а в каждом чипе — несколько банков памяти, прежде всего необходимо указать, в каком чипе и банке находится ячейка. Для этого используют специальные сигналы CS, BA0 и BA1.

Сигнал CS позволяет выбрать требуемый чип памяти. Когда сигнал активен, возможен доступ к чипу памяти, то есть чип активируется. В противном случае чип памяти недоступен.

Сигналы BA0 и BA1 позволяют адресовать один из четырех банков памяти. Учитывая, что каждый сигнал может принимать одно из двух значений: 0 или 1, комбинации 00, 01, 10 и 11 позволяют задать адрес четырех банков памяти.

Когда выбраны чип и банк памяти, можно получить доступ к требуемой ячейке памяти, задав адрес столбца и строки. Адрес строки и столбца передается по специальной мультиплексированной шине адреса MA (Multiplexed Address).

Для считывания адреса строки на входы матрицы памяти подается специальный стробирующий импульс RAS (Row Address Strobe). Если точнее, то этот импульс представляет собой изменение уровня сигнала с высокого на низкий, то есть при переходе сигнала RAS с высокого уровня на низкий возможно считывание адреса строки.

При этом отметим, что само считывание адреса строки происходит не в момент изменения RAS-сигнала, а синхронизовано с положительным фронтом тактирующего импульса.

Аналогичным образом считывание адреса столбца происходит при изменении уровня сигнала (стробирующего импульса) CAS# (Column Address Strobe) с высокого значения на низкое и синхронизовано с положительным фронтом тактирующего импульса.

Кстати, заметим, что, поскольку все события памяти (считывание адреса строки и столбца, выдача или запись данных) синхронизованы с фронтами тактирующего импульса, память называется синхронной.

Импульсы RAS# и CAS# подаются последовательно друг за другом, причем импульс CAS# всегда следует за импульсом RAS#, то есть сначала происходит выбор строки, а затем — выбор столбца.

После считывания адреса строки и столбца ячейки памяти к ней возможен доступ для чтения или записи информации. Эти операции подобны друг другу, но для записи используется специальный разрешающий сигнал (стробирующий импульс) WE# (Write Enable). Если сигнал по напряжению меняется с высокого уровня на низкий, то в выбранную ячейку происходит запись информации. Если же сигнал WE# остается высоким, то происходит считывание информации с выбранной ячейки.

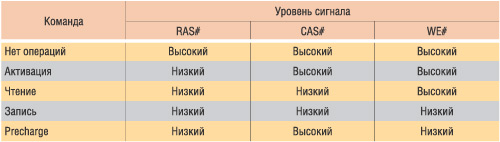

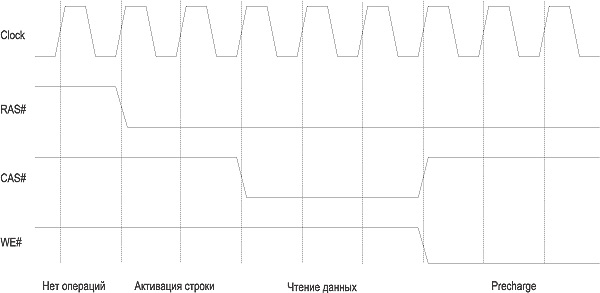

После того как все данные записаны или считаны с ячеек активной сроки, необходимо выполнить команду Precharge, которая закрывает активную строку и позволяет активировать следующую строку. Команды, используемые для записи или чтения, и соответствующие им состояния стробирующих импульсов представлены в табл. 1 и на рис. 2.

Таблица 1. Команды, используемые для записи или чтения ячеек памяти

Рис. 2. Диаграмма команд RAM-памяти

Характеристики памяти

ак известно, главной характеристикой памяти является ее пропускная способность, то есть максимальное количество данных, которое можно считать из памяти или записать в память в единицу времени. Именно эта характеристика прямо или косвенно отражается в названии типа памяти.

ак известно, главной характеристикой памяти является ее пропускная способность, то есть максимальное количество данных, которое можно считать из памяти или записать в память в единицу времени. Именно эта характеристика прямо или косвенно отражается в названии типа памяти.

Для того чтобы определить пропускную способность памяти, нужно умножить частоту системной шины на количество байт, передаваемых за один такт. Память SDRAM имеет 64-битную (8-байтную) шину данных.

К примеру, память DDR400 имеет пропускную способность 400 МГц x 8 байт = 3,2 Гбайт/с. Если память работает в двухканальном режиме, то теоретическая пропускная способность памяти удваивается, то есть для памяти DDR400 в двухканальном режиме она составляет 6,4 Гбайт/с. Теоретическая пропускная способность для различных типов памяти отображена в табл. 2.

Таблица 2. Соответствие типа памяти и теоретической пропускной способности

Казалось бы, чем больше пропускная способность памяти, тем лучше. Отчасти это справедливо, но лишь отчасти. Дело в том, что пропускная способность памяти должна быть сбалансирована с пропускной способностью процессорной шины. И если пропускная способность памяти превосходит пропускную способность процессорной шины, то именно процессорная шина становится узким местом в системе, ограничивая возможности памяти. Если рассматривать процессор Intel Pentium 4 или новые двухъядерные процессоры Intel Pentium D, то тактовая частота процессорной шины составляет 800 или 1066 МГц. Учитывая, что ширина шины составляет 64 бит (или 8 байт), получаем, что пропускная способность процессорной шины составляет 6,4 или 8,5 Гбайт/с. Из этого следует, что если в системе используется процессор с частотой FSB 800 МГц, то в одноканальном режиме для сбалансированного решения достаточно использовать память DDR2-800, а в двухканальном — DDR2-400.

Аналогичным образом, если в системе используется процессор с частотой FSB 1066 МГц, то в одноканальном режиме для сбалансированного решения потребуется использовать память DDR2-1066, а в двухканальном — достаточно памяти DDR2-533.

С учетом того, что типичной ситуацией является использование памяти в двухканальном режиме, память DDR2-533 вполне обеспечивает сбалансированное решение.

Возникает вопрос: если память DDR2-533 обеспечивает пропускную способность, согласующуюся с пропускной способностью процессорной шины, зачем тогда нужна более быстродействующая память? Дело в том, что до сих пор мы говорили лишь о теоретической, то есть о максимально возможной пропускной способности, которая реализуется только в случае последовательной передачи данных — когда данные передаются с каждым тактом. В реальной ситуации теоретический предел недостижим, поскольку, кроме этого, необходимо учитывать и такты, которые необходимы для получения доступа к самой ячейке памяти, а также для настроек модуля памяти. В связи с этим другими важными характеристиками памяти являются тайминги памяти или ее латентность.

Под латентностью принято понимать задержку между поступлением команды и ее реализацией. В этом смысле латентность можно сравнить с телефонным звонком. Время, которое проходит от набора номера (вызова абонента) и до ответа в трубке, — это и есть латентность телефонного вызова.

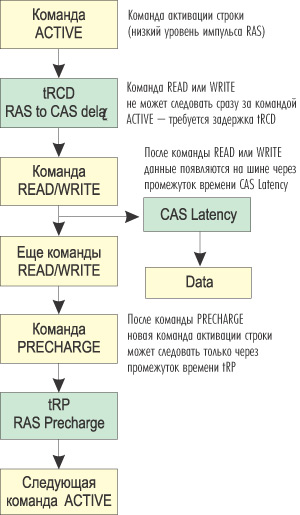

Латентность памяти, которая определяется ее таймингами, — это задержки, измеряемые в количествах тактов, между отдельными командами. Рассмотрим тайминги памяти более подробно. На рис. 3 показана последовательность команд при чтении или записи данных в память. Первоначально происходит активация нужной строки памяти (команда ACTIVE), для чего сигнал RAS переводится в низкий уровень и происходит считывание адреса строки. Далее следует команда записи (WRITE) или чтения (READ) данных, для чего сигнал CAS переводится в низкий уровень и в надлежащий уровень устанавливается сигнал WE. При установке CAS в низкий уровень после прихода положительного фронта тактирующего импульса происходит выборка адреса столбца, наличествующего в данный момент на шине адреса, и открывается доступ к нужному столбцу матрицы памяти. Однако команда чтения или записи не может следовать непосредственно за командой активации — требуется, чтобы между этими командами, то есть между импульсами RAS и CAS, существовал некий промежуток времени RAS to CAS Delay (задержка сигнала CAS относительно сигнала RAS). Эту задержку, измеряемую в тактах системной шины, принято обозначать tRCD.

Рис. 3. Блок-схема последовательности команд RAM-памяти

После команды чтения (записи) данных и до выдачи первого элемента данных на шину (записи данных в ячейку памяти) проходит промежуток времени, который называется CAS Latency. Эта задержка измеряется в тактах системной шины и обозначается tCL. Каждый последующий элемент данных появляется на шине данных в очередном такте.

Завершение цикла обращения к банку памяти осуществляется подачей команды PRECHARGE, приводящей к закрытию строки памяти. После команды PRECHARGE и до поступления новой команды активации строки памяти должен пройти промежуток времени (tRP), называемый Row Precharge.

Еще один тип задержки, называемый ACTIVE to PRECHARGE delay, — это промежуток времени между командой активации строки памяти и командой PRECHARGE. Эта задержка обозначается tRAS и измеряется в тактах системной шины.

Ну и последний тип задержки, который необходимо упомянуть, — это скорость выполнения команд (Command Rate). Command Rate — это задержка в тактах системной шины между командой CS# выбора чипа и командой активации строки. Как правило, задержка Command Rate составляет один или два такта (1T или 2T).

Описанные задержки — RAS to CAS Delay (tRCD), CAS Latency (tCL) и Row Precharge (tRP) — определяют тайминги памяти, записываемые в виде последовательности tCL—tRCD—tRP—tRAS—Command Rate. К примеру, для модуля DDR400 (PC3200) тайминги могут быть следующими: 2-3-4-5-(1T). Это означает, что для данного модуля CAS Latency (tCL) составляет 2 такта, RAS to CAS Delay (tRCD) — 3 такта, Row Precharge (tRP) — 4 такта, ACTIVE to PRECHARGE delay (tRAS) — 5 тактов и Command Rate — 1 такт.

Понятно, что чем меньше тайминги, тем более быстродействующей является память. Поэтому если сравнивать память с таймингом 3-3-3-5-(1T) и память с таймингом 3-2-2-5-(1T), то последняя оказывается более быстродействующей.

Память SDR

азобравшись с такими важными характеристиками памяти, как ее тайминги, можно перейти непосредственно к принципам работы памяти. Несмотря на то что данная статья посвящена современной памяти DDR2, рассмотрение принципов работы памяти мы начнем с синхронной SDRAM-памяти типа SDR (Single Data Rate).

азобравшись с такими важными характеристиками памяти, как ее тайминги, можно перейти непосредственно к принципам работы памяти. Несмотря на то что данная статья посвящена современной памяти DDR2, рассмотрение принципов работы памяти мы начнем с синхронной SDRAM-памяти типа SDR (Single Data Rate).

В SDR SDRAM-памяти обеспечивается синхронизация всех входных и выходных сигналов с положительными фронтами импульсов тактового генератора. Весь массив памяти SDRAM-модуля разделен на два независимых банка. Такое решение позволяет совмещать выборку данных из одного банка с установкой адреса в другом банке, то есть одновременно иметь две открытые страницы. Доступ к этим страницам чередуется (bank interleaving), и соответственно устраняются задержки, что обеспечивает создание непрерывного потока данных.

Наиболее распространенными типами SDRAM-памяти до недавнего времени являлись PC100 и PC133. Цифры 100 и 133 определяют частоту системной шины в мегагерцах (МГц), которую поддерживает эта память. По внутренней архитектуре, способам управления и внешнему дизайну модули памяти PC100 и PC133 полностью идентичны.

В SDRAM-памяти организована пакетная обработка данных, что позволяет производить обращение по новому адресу столбца ячейки памяти на каждом тактовом цикле. В микросхеме SDRAM имеется счетчик для наращивания адресов столбцов ячеек памяти, чтобы обеспечить быстрый доступ к ним.

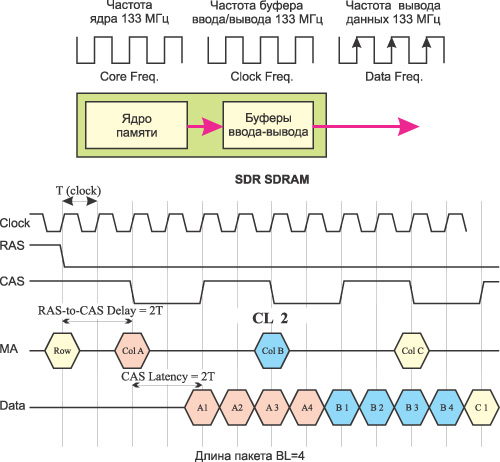

В SDRAM-памяти ядро и буферы обмена работают в синхронном режиме на одной и той же частоте (100 или 133 МГц). Передача каждого бита из буфера происходит с каждым тактом работы ядра памяти.

Временная диаграмма работы памяти SDR SDRAM показана на рис. 4.

Рис. 4. Временная диаграмма работы SDR SDRAM-памяти

Память DDR

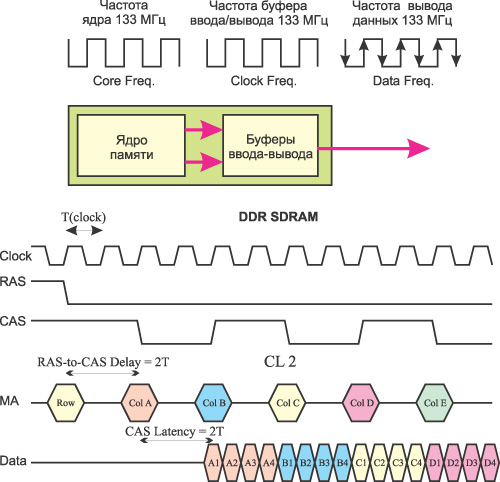

амять DDR SDRAM, которая пришла на смену памяти SDR, обеспечивает в два раза большую пропускную способность. Аббревиатура DDR (Double Data Rate) в названии памяти означает удвоенную скорость передачи данных. В DDR-памяти каждый буфер ввода-вывода передает два бита за один такт, то есть фактически работает на удвоенной тактовой частоте, оставаясь при этом полностью синхронизированным с ядром памяти. Такой режим работы возможен в случае, если эти два бита доступны буферу ввода-вывода на каждом такте работы памяти. Для этого требуется, чтобы каждая команда чтения приводила к передаче из ядра памяти в буфер сразу двух бит. С этой целью используются две независимые линии передачи от ядра памяти к буферам ввода-вывода, откуда биты поступают на шину данных в требуемом порядке.

амять DDR SDRAM, которая пришла на смену памяти SDR, обеспечивает в два раза большую пропускную способность. Аббревиатура DDR (Double Data Rate) в названии памяти означает удвоенную скорость передачи данных. В DDR-памяти каждый буфер ввода-вывода передает два бита за один такт, то есть фактически работает на удвоенной тактовой частоте, оставаясь при этом полностью синхронизированным с ядром памяти. Такой режим работы возможен в случае, если эти два бита доступны буферу ввода-вывода на каждом такте работы памяти. Для этого требуется, чтобы каждая команда чтения приводила к передаче из ядра памяти в буфер сразу двух бит. С этой целью используются две независимые линии передачи от ядра памяти к буферам ввода-вывода, откуда биты поступают на шину данных в требуемом порядке.

Поскольку при таком способе организации работы памяти происходит предвыборка двух бит перед передачей их на шину данных, его также называют Pre-fetch 2 (предвыборка 2).

Для того чтобы осуществить синхронизацию работы ядра памяти и буферов ввода-вывода, используется одна и та же тактовая частота (одни и те же тактирующие импульсы). Только если в самом ядре памяти синхронизация осуществляется по положительному фронту тактирующего импульса, то в буфере ввода-вывода для синхронизации используется как положительный, так и отрицательный фронт тактирующего импульса (рис. 5). Таким образом, передача двух бит в буфер ввода-вывода по двум раздельным линиям осуществляется по положительному фронту тактирующего импульса, а их выдача на шину данных происходит как по положительному, так и по отрицательному фронту тактирующего импульса. Это обеспечивает в два раза более высокую скорость работы буфера и соответственно вдвое большую пропускную способность памяти (см. рис. 5).

Рис. 5. Временная диаграмма работы DDR SDRAM-памяти

Все остальные принципиальные характеристики DDR-памяти не изменились: структура нескольких независимых банков позволяет совмещать выборку данных из одного банка с установкой адреса в другом банке, то есть можно одновременно иметь две открытые страницы. Доступ к этим страницам чередуется (bank interleaving), что приводит к устранению задержек и обеспечивает создание непрерывного потока данных.

Память DDR2

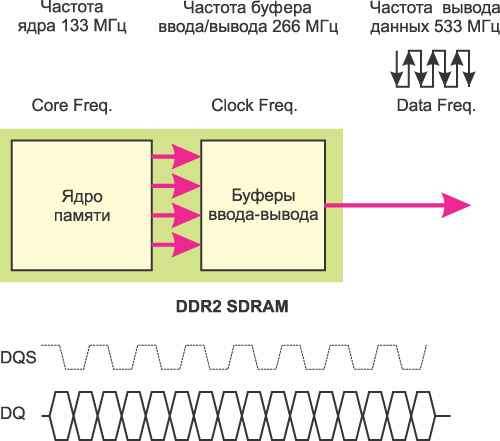

сли следовать терминологии SDR (Single Data Rate), DDR (Double Data Rate), то память DDR2 было бы логично назвать QDR (Quadra Data Rate), поскольку этот стандарт подразумевает в четыре раза большую скорость передачи, то есть в стандарте DDR2 при пакетном режиме доступа данные передаются четыре раза за один такт. Для организации данного режима работы памяти необходимо, чтобы буфер ввода-вывода работал на учетверенной частоте по сравнению с частотой ядра памяти. Достигается это следующим образом: ядро памяти, как и прежде, синхронизируется по положительному фронту тактирующих импульсов, а с приходом каждого положительного фронта по четырем независимым линиям в буфер ввода-вывода передаются четыре бита информации (выборка четырех битов за такт). Сам буфер ввода-вывода тактируется на удвоенной частоте ядра памяти и синхронизируется как по положительному, так и по отрицательному фронту этой частоты. Иными словами, с приходом положительного и отрицательного фронтов происходит передача битов в мультиплексном режиме на шину данных (рис. 6). Это позволяет за каждый такт работы ядра памяти передавать четыре бита на шину данных, то есть вчетверо повысить пропускную способность памяти.

сли следовать терминологии SDR (Single Data Rate), DDR (Double Data Rate), то память DDR2 было бы логично назвать QDR (Quadra Data Rate), поскольку этот стандарт подразумевает в четыре раза большую скорость передачи, то есть в стандарте DDR2 при пакетном режиме доступа данные передаются четыре раза за один такт. Для организации данного режима работы памяти необходимо, чтобы буфер ввода-вывода работал на учетверенной частоте по сравнению с частотой ядра памяти. Достигается это следующим образом: ядро памяти, как и прежде, синхронизируется по положительному фронту тактирующих импульсов, а с приходом каждого положительного фронта по четырем независимым линиям в буфер ввода-вывода передаются четыре бита информации (выборка четырех битов за такт). Сам буфер ввода-вывода тактируется на удвоенной частоте ядра памяти и синхронизируется как по положительному, так и по отрицательному фронту этой частоты. Иными словами, с приходом положительного и отрицательного фронтов происходит передача битов в мультиплексном режиме на шину данных (рис. 6). Это позволяет за каждый такт работы ядра памяти передавать четыре бита на шину данных, то есть вчетверо повысить пропускную способность памяти.

Рис. 6. Временная диаграмма работы памяти DDR2 SDRAM

По сравнению с памятью DDR, память DDR2 позволяет обеспечить ту же пропускную способность, но при вдвое меньшей частоте ядра. К примеру, в памяти DDR400 ядро функционирует на частоте 200 МГц, а в памяти DDR2-400 — на частоте 100 МГц. В этом смысле память DDR2 имеет значительно большие потенциальные возможности для увеличения пропускной способности по сравнению с памятью DDR.

От теории к практике: память DDR2-667 Kingmax KLCD48F-A8EB5-ECAS

зучив теоретические аспекты функционирования современной памяти DDR2, перейдем от теории к практике. В качестве примера мы рассмотрим новую память SDRAM DDR2-667 компании Kingmax. Стенд для тестирования имел следующую конфигурацию:

зучив теоретические аспекты функционирования современной памяти DDR2, перейдем от теории к практике. В качестве примера мы рассмотрим новую память SDRAM DDR2-667 компании Kingmax. Стенд для тестирования имел следующую конфигурацию:

- процессор: Intel Pentium 4 570 (тактовая частота 3,8 ГГц, кэш L2 1 Мбайт);

- частота FSB: 800 МГц;

- материнская плата: MSI P4N Diamond;

- чипсет: NVIDIA nForce4 SLI Intel Edition;

- память: два модуля DDR2-667 Kingmax KLCD48F-A8EB5-ECAS объемом по 1 Гбайт каждый (двухканальный режим работы);

- видеокарта: MSI NX6800 Ultra-T2D512E.

К сожалению, технической информации о модулях Kingmax KLCD48F-A8EB5-ECAS на сайте производителя маловато. Единственное, что удалось узнать, так это об организации модуля (8Ѕ128 Мбайт) и о значении параметра CAS Latency, которое составляет 5 тактов.

Для тестирования памяти мы использовали тестовый пакет RightMark Memory Analyzer v 3.55 и набор игровых бенчмарков: Half-Life 2, DOOM 3, FarCry 1.3, Unreal Tournament 2004 и 3DMark 2003. С целью увеличения нагрузки на процессор и память при тестировании использовалось разрешение 640Ѕ480 точек, а драйвер видеокарты настраивался на максимальную производительность.

Как выяснилось в процессе тестирования, модули памяти KLCD48F-A8EB5-ECAS имеют тайминги по умолчанию (by SPD) и составляют последовательность 5-5-5-13-(2T). Таким образом:

• CAS Latency (tCL) — 5T;

• RAS to CAS delay (tRCD) — 5T;

• Row Precharge (tRP) — 5T;

• Active to Precharge (tRAS) — 13T;

• Command Rate — 2T.

Для того чтобы оценить потенциальные возможности модулей памяти по разгону (но без ущерба для стабильности), мы также провели тестирование в режиме с наименьшими таймингами, которые были определены методом проб и ошибок. Как выяснилось, минимальные тайминги, которые поддерживают данные модули памяти на тактовой частоте 667 МГц, составляют последовательность 4-3-3-5-(2T). Кроме того, мы провели разгон памяти по тактовой частоте, чтобы оценить максимально возможную тактовую частоту, поддерживаемую данными модулями при работе в двухканальном режиме.

Для тестирования с использованием тестового пакета RightMark Memory Analyzer v 3.55 использовались встроенные в бенчмарк пресеты:

• RAM Performance Stream;

• Average Memory Bandwidth, SSE2;

• Maximal RAM Bandwidth, Software Prefetch, SSE2;

• Average RAM Latency;

• Minimal RAM Latency, 16 Mbyte Block, L1 Cache line.

С подробным описанием каждого пресета можно ознакомиться на сайтах www.rightmark.org или www.ixbt.com.

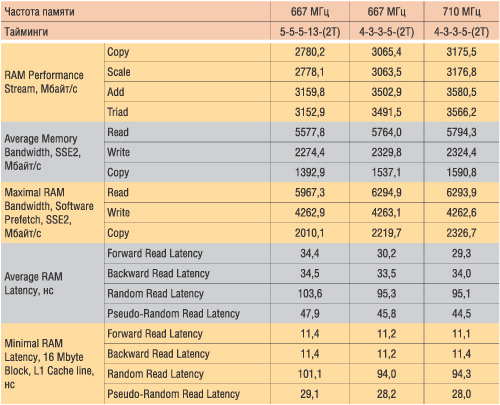

Результаты тестирования с использованием тестового пакета RightMark Memory Analyzer v 3.55 представлены в табл. 3.

Таблица 3. Результаты тестирования модулей KLCD48F-A8EB5-ECAS в двухканальном режиме

с использованием тестового пакета RightMark Memory Analyzer v 3.55

Как следует из результатов тестирования, тайминги по умолчанию (by SPD) являются сильно завышенными. Уменьшение таймингов не оказывает влияния на стабильность работы модулей памяти, однако приводит к значительному увеличению пропускной способности памяти и к снижению латентности. Так, максимальная пропускная способность памяти при таймингах 5-5-5-13-(2T) составляет 5967,3 Мбайт/с (операция чтения, пресет Maximal RAM Bandwidth, Software Prefetch, SSE2). В то же время при уменьшении таймингов до 4-3-3-5-(2T) пропускная способность увеличивается до 6294,9 Мбайт/с, то есть на 5,5%. Отметим, что значение 6294,9 Мбайт/с близко к теоретическому пределу пропускной способности процессорной шины, которая в данном случае составляет 6,4 Гбайт/с.

Увеличение тактовой частоты до 710 МГц не оказывает влияния на стабильность в работе памяти, однако добиться значительного увеличения производительности памяти в данном случае не удается, что еще раз подтверждает тот факт, что изменение таймингов памяти оказывает существенно большее влияние на производительность памяти, нежели увеличение тактовой частоты.

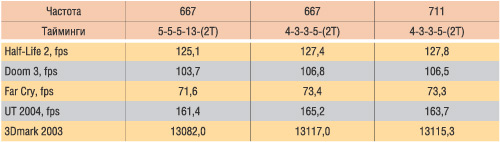

Теперь обратимся к результатам игровых тестов (табл. 4). Как видите, уменьшение таймингов памяти позволяет (хотя и незначительно) увеличить результаты во всех игровых тестах. В то же время увеличение тактовой частоты памяти никак не отражается на результатах теста.

Таблица. 4. Результаты тестирования модулей памяти KLCD48F-A8EB5-ECAS в двухканальном режиме в игровых приложениях

***

Итак, если говорить о рассмотренных модулях памяти Kingmax KLCD48F-A8EB5-ECAS, то можно констатировать, что в сочетании с материнской платой MSI P4N Diamond, а следовательно, и с чипсетом NVIDIA nForce4 SLI Intel Edition, эти модули обеспечивают гарантированно стабильную работу и прекрасно разгоняются путем уменьшения таймингов. Именно поэтому мы решили присвоить модулям Kingmax KLCD48F-A8EB5-ECAS знак «Редакция рекомендует».

Редакция выражает признательность компании Kingmax (www.kingmax.com) за предоставление модулей памяти Kingmax KLCD48F-A8EB5-ECAS.