Интегрированные транзисторы CMOS tri-gate

Подготовка к созданию технологий будущего поколения

Новая конструкция транзисторов CMOS — выход в третье измерение

Усовершенствование конструкции благодаря объединению инноваций

Технология создания напряжений

Чтобы обеспечить соответствие закону Мура и размещать на кристалле все больше транзисторов, полупроводниковая промышленность продолжает внедрять технологические инновации, направленные на уменьшение размеров транзисторов. Однако, несмотря на развитие технологий будущего, уменьшение размеров транзисторов становится все более проблематичным, в частности из-за ухудшения эффектов коротких каналов и возрастания паразитных утечек при уменьшении размеров затвора. Утечка как транзистора в закрытом состоянии (возрастающая при уменьшении размеров затвора), так и диэлектрика затвора (возрастающая при уменьшении толщины слоя диэлектрика затвора) вызывает увеличение рассеиваемой мощности при масштабировании.

Для решения проблемы утечки транзисторов в закрытом состоянии в 2002 году корпорация Intel разработала первый в мире транзистор CMOS tri-gate, в котором применялась новаторская трехмерная конструкция затвора, позволяющая повысить управляющий ток и снизить ток утечки транзистора в закрытом состоянии. С тех пор компания Intel добилась улучшения эксплуатационных характеристик транзисторов и эффективности использования электроэнергии путем объединения конструкции tri-gate с другими кремниевыми производственными технологиями и инновационными материалами, включая напряженный кремний, диэлектрики затвора high-k, металлические электроды затвора и эпитаксиальные рельефные истоки/стоки. В результате был создан непланарный транзистор, который обеспечивает увеличение управляющего тока на 30% для транзисторов NMOS и на 60% для транзисторов PMOS по сравнению с оптимизированными передовыми 65-нм планарными транзисторами при том же уровне утечки в закрытом состоянии. Этот результат показывает, что преимущества различных полупроводниковых инноваций дополняют друг друга и их можно объединять, чтобы расширять и продолжать тенденции масштабирования и увеличения производительности транзисторов CMOS.

Новая конструкция транзисторов CMOS — выход в третье измерение

С момента появления в конце 1950-х годов планарные транзисторы являются основным компонентом микропроцессоров. Для уменьшения размеров планарного транзистора необходимо сокращать толщину диэлектрика затвора и перехода исток/сток. Однако, поскольку уменьшать эти элементы транзисторов становится все труднее, сокращают длину затвора. При масштабировании же планарных транзисторов за счет уменьшения длины затвора ухудшаются электростатические характеристики и эксплуатационные характеристики короткого канала.

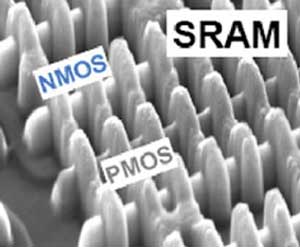

Новая архитектура транзистора, которая позволяет значительно улучшить электростатические и эксплуатационные характеристики короткого канала, — так называемый транзистор tri-gate — показана на рис. 1. Этот транзистор может быть изготовлен как на подложке SOI (кремний на изоляторе), так и на стандартной подложке из кристаллического кремния. В нем применяются один электрод затвора в верхней части канала и два электрода затвора по бокам канала. Транзистор с верхним затвором имеет физическую длину затвора LG и физическую ширину затвора WSi, а транзистор с боковым затвором — физическую длину затвора LG и физическую ширину затвора HSi (рис. 1).

Рис. 1. В транзисторе Intel tri-gate затворы окружают кремниевый канал с трех или четырех сторон

Вообще, электростатика, а следовательно, и производительность короткого канала транзистора tri-gate определяются отношением фактического значения LG к фактическому значению WSi. Масштабирование WSi обеспечивает дополнительное улучшение электростатики транзистора совместно с масштабированием LG, а также с масштабированием перехода исток/сток и диэлектрика затвора. Общий групповой управляющий ток транзистора равен сумме управляющих токов транзистора с верхним затвором и двух транзисторов с боковыми затворами, или 2HSi +WSi. Таким образом, чем выше транзистор, тем больше общий групповой управляющий ток.

Усовершенствование конструкции благодаря объединению инноваций

Для ускорения переключения и снижения тепловыделения непланарных транзисторов корпорация Intel продолжила усовершенствование конструкции tri-gate, объединив ее с несколькими передовыми полупроводниковыми технологиями.

Технология создания напряжений

Технология напряжений используется при изготовлении транзисторов NMOS и PMOS по 90- и 65-нм техпроцессам для улучшения их эксплуатационных характеристик. Эта же технология применяется и для непланарной архитектуры tri-gate. Технология создания напряжений позволяет увеличить подвижность как электронов, так и дырок и повышает скорость переключения транзисторов CMOS.

Затвор High-k/metal

В транзисторах CMOS tri-gate для изготовления диэлектрического слоя затвора используется материал high-k (с высоким значением k — диэлектрической постоянной) вместо традиционного диэлектрика из диоксида кремния. А электроды затвора вместо традиционного поликристаллического кремния изготавливаются из металла. Применение затвора high-k/metal позволяет снизить утечку диэлектрика затвора по сравнению со стандартным затвором из диоксида кремния/поликристаллического кремния. Использование металлических электродов устраняет истощение поликристаллического кремния и улучшает эксплуатационные характеристики транзистора. Кроме того, применение металлических электродов с работой выхода, близкой к середине ширины запрещенной энергетической зоны, позволяет снизить концентрацию примесей в подложке, что повышает подвижность транзистора, а следовательно, улучшает его общие эксплуатационные характеристики.

Двойная эпитаксиальная рельефная структура истока/стока

В комплексных транзисторах CMOS tri-gate используется уникальная рельефная структура истока/стока, построенная с помощью эпитаксиального нанесения кремния для транзисторов NMOS и кремния-германия для транзисторов PMOS. Области истока и стока возвышаются над плоскостью поверхности соединения затвора с подложкой из оксида кремния. Это позволяет снизить паразитное сопротивление и улучшить эксплуатационные характеристики транзистора.

Корпорация Intel изготовила прототипы комплексных транзисторов CMOS tri-gate как на подложках SOI, так и на подложках из кристаллического кремния. Транзисторы tri-gate на подложке из кристаллического кремния и на подложке SOI демонстрируют эквивалентные возможности масштабирования и производительность короткого канала, а также величину управляющего тока.

Комплексные транзисторы Tri-Gate позволяют повысить производительность

В тестах на производительность корпорация Intel продемонстрировала, что комплексные транзисторы tri-gate NMOS и PMOS показали отличное управление эффектами короткого канала (short channel effects, SCE), что позволяет уменьшить паразитные утечки и снизить энергопотребление. Транзисторы tri-gate также продемонстрировали более высокую производительность с точки зрения управляющего тока по сравнению с оптимизированными современными планарными 65-нм транзисторами (рис. 2). Для заданного тока утечки транзистора в закрытом состоянии (IOFF) управляющий ток (IDSAT) комплексного транзистора tri-gate NMOS на 30% выше по сравнению с планарным транзистором. Этот эффект еще более отчетливо проявляется в случае комплексного транзистора tri-gate PMOS, который имеет IDSAT на 60% выше, чем у планарного транзистора, при заданном значении IOFF.

Рис. 2. Комплексные транзисторы tri-gate NMOS и PMOS

демонстрируют рекордные значения управляющего тока.

Значение управляющего тока (IDSAT) нормализовано к общей ширине элемента, например 2HSi + WSi

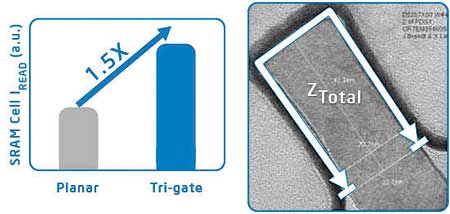

Корпорация Intel также изготовила рабочий прототип ячеек статической памяти (SRAM) tri-gate (рис. 3). Ток считывания ячейки такой памяти в 1,5 раза выше, чем у стандартной планарной ячейки SRAM. Как показано на рис. 4, архитектура tri-gate обеспечивает большее значение ширины элемента для заданной площади ячейки по сравнению со стандартным планарным транзистором — это гарантирует более высокий управляющий ток, поскольку общий ток прямо пропорционален общей ширине элемента.

Рис. 3. Внешний вид ячеек памяти tri-gate SRAM

Рис. 4. Ячейки памяти tri-gate SRAM имеют ток считывания в 1,5 раза больше,

чем стандартные планарные ячейки SRAM эквивалентного размера

благодаря большему значению ширины элемента ZTOTAL> = 2HSi + WSi

Заключение

С уменьшением размеров транзисторов паразитные токи утечки и рассеяние мощности становятся серьезными проблемами. Объединив новаторскую конструкцию трехмерных транзисторов tri-gate с передовыми полупроводниковыми технологиями, такими как напряженный кремний и затвор high-k/metal, корпорация Intel создала инновационный подход для решения проблем утечки тока и повышения эксплуатационных характеристик полупроводниковых устройств.

Комплексные транзисторы tri-gate CMOS будут играть важнейшую роль в концепции энергосберегающей производительности корпорации Intel, так как они имеют меньший ток утечки и потребляют меньше электроэнергии по сравнению с планарными транзисторами.

Благодаря тому что транзисторы tri-gate позволяют существенно повысить производительность и эффективность использования электроэнергии, они обеспечивают возможность дальнейшего уменьшения размеров кремниевых транзисторов. Транзисторы tri-gate могут стать основным компонентом микропроцессоров в будущем. Эту технологию можно применять в экономичном, крупносерийном производственном процессе по созданию высокопроизводительной и энергосберегающей продукции.