Весенний форум IDF 2008

Новый процессор Intel Atom и процессорная технология Intel Centrino Atom

От ноутбуков к нетбукам и неттопам

Ультрамобильная платформа следующего поколения Moorestown

Montevina и Calpella — платформы для ноутбуков следующего поколения

Ядро процессора на базе микроархитектуры Nehalem

2-3 апреля в Шанхае (Китай) прошел очередной весенний Форум компании Intel для разработчиков (Intel Developer Forum, IDF).

По устоявшейся традиции Форум компании Intel для разработчиков на протяжении многих лет проводится два раза в год — весной и осенью. Традиционно центральные осенние и весенние форумы давали старт целой серии региональных форумов, которые проходили в разных странах мира. В частности, несколько раз форумы IDF проходили и в России, в Москве. Однако начиная с 2007 года компания Intel существенно сократила бюджет на проведение форумов, в связи с чем их количество резко уменьшилось. Сегодня общее количество форумов IDF ограничивается тремя. Один из них проводится в США, а остальные два — в Китае. В частности, в этом году весенний форум прошел в Шанхае, а осенний будет проводиться 19-21 августа в Сан-Франциско, а затем 20-21 октября в Тайпее (Тайвань).

Казалось бы, это не очень справедливо. Однако не стоит забывать, что Китай — великая страна, и тот факт, что именно в Китае, а не в какой-либо другой стране проводятся важнейшие мероприятия корпорации Intel, имеет веские основания. Во-первых, именно в Китае сосредоточена практически вся мировая ИT-индустрия, во-вторых, Китай был, есть и будет рынком номер один в мире. А потому понятно, что точно так же, как для Америки усиление своего влияния в Украине и Грузии является приоритетной задачей национальной безопасности (любят эти американцы красивые слава), для корпорации Intel приоритетной задачей является усиление своего присутствия на китайском рынке. Причем Китай — это не Грузия и даже не Украина, и подмять его под себя просто так не получится, приходится действовать тонкими дипломатическими методами, поэтому проведение IDF в Китае даже чаще, чем в США, — это один из способов усилить свое присутствие на китайском рынке.

Открытие весеннего форума IDF 2008 в Шанхае

Впрочем, свое неравнодушное отношение к Китаю компания Intel демонстрирует уже не первый год. В частности, где бы ни проводился IDF, для китайских участников форума (только для них!) всегда организуется синхронный перевод с английского языка. Казалось бы, мелочь, но если задуматься, факт этот весьма красноречивый.

Стремление Intel укрепить свои позиции в Китае вполне может вызвать и негативные последствия. Сегодня топ-менеджеры различных правительственных и коммерческих китайских компаний, говоря традиционные слова благодарности в адрес компании Intel (Intel инвестирует крупные средства в китайские компании), отмечают, что Китай развивается вместе с Intel, что вполне справедливо. Но, как знать, возможно, не Китай будет развиваться вместе с Intel, а, наоборот, Intel будет развиваться вместе с Китаем, а спустя еще какое-то время китайцы с невозмутимым спокойствием и улыбкой на лице заявят примерно следующее: «Спасибо, но мы уже все умеем и вы нам больше не нужны». Впрочем, время покажет… А пока вернемся к китайскому IDF.

Форум в китайском стиле

Вообще, изначально IDF зарождался как форум для разработчиков. Собственно, именно так и расшифровывается аббревиатура IDF — Intel Developer Forum. Однако постепенно это мероприятие трансформировалось из технического форума в некое подобие консьюмерского шоу, которое явно не ориентировано на разработчиков, так что сегодня от Developer Forum осталось лишь название. Что делать, но это своеобразная тенденция времени: чем сложнее становится техника, тем менее интересны пользователям принципы ее функционирования. А потому появление на сцене Патрика Гелсингера (Pat Gelsinger), старшего вице-президента Intel и генерального менеджера подразделения Digital Enterprise Group, в роли короля обезьян удивления не вызвало. И если бы не технические семинары и круглые столы, которые проходили в рамках IDF и были посвящены технологиям и новым продуктом Intel, то информационная составляющая форума оказалась бы довольно скудной. Потому мы не станем заниматься нудным пересказом ключевых докладов топ-менеджеров Intel, а попытаемся выделить из этих сообщений основную информационную составляющую и детализировать эту общую информацию теми подробностями, которые можно было почерпнуть из технических семинаров. Кроме того, насколько это возможно, постараемся дать и свои комментарии.

Старший вице-президент Intel

и генеральный менеджер подразделения

Digital Enterprise Group Патрик

Гелсингер в роли короля обезьян

По сложившейся традиции на форуме освещался широкий круг вопросов, связанных с продукцией и технологиями Intel. Рассматривались новые процессорные микроархитектуры, технологии и тенденции развития мобильных, серверных и настольных платформ, разработка многопоточных приложений, разработка ультрамобильных платформ, разработка ПО, управление электропитанием и охлаждением, технологии увеличения времени автономной работы мобильных устройств и т.д. Естественно, осветить все темы, затронутые на форуме, в рамках одной статьи нереально. Поэтому рассмотрим лишь наиболее интересные, с нашей точки зрения, вопросы и подробно расскажем о новом процессоре Atom и новой платформе Atom Centrino для мобильных интернет-устройств (Mobile Internet Device, MID), микроархитектуре следующего поколения Nehalem, остановимся на тенденциях развития мобильных платформ и, в частности, поговорим о новой концепции мобильных платформ Nettwork.

Новый процессор Intel Atom и процессорная технология Intel Centrino Atom

Одной из центральных тем IDF стал новый процессор Intel Atom, а также процессорная технология Intel Centrino Atom для мобильных интернет-устройств (MID) и встраиваемых вычислительных решений.

Напомним, что впервые о MID-устройствах мы услышали на весеннем форуме IDF 2007 в Пекине. И если до этого под ультрамобильными платформами понимался класс устройств, известный как UMPC (Ultra Mobile PC), то теперь ультрамобильные платформы дополнились еще и MID-устройствами (Mobile Internet Device). Хотя сказать «дополнились» в данном случае вряд ли возможно. UMPC так и не получили широкого распространения (во всяком случае в России), и, несмотря на попытки Intel концептуально разделить UMPC и MID, устройства MID в скором времени полностью заменят на UMPC. Недаром, говоря об ультрамобильных платформах, старший вице-президент Intel и генеральный менеджер подразделения Ultra Mobility Group корпорации Intel Ананд Чандрасехер (Anand Chandrasekher) делал упор именно на MID-устройствах, а о UMPC не сказал практически ни слова. Похоже, у UMPC просто нет будущего.

Старший вице-президент Intel и генеральный менеджер подразделения

Ultra Mobility Group корпорации Intel Ананд Чандрасехер

рассказывает

о светлом будущем MID-устройств

MID — это действительно мобильные устройства карманного формата, способные предоставить самый удобный способ подключения к Интернету. MID-устройства позволят пользователям общаться, развлекаться, получать доступ к информации, продуктивно работать в пути и, как ожидается, станут основой нового класса потребительской техники следующего поколения: портативных интернет-видеоплееров, навигаторов, конвергентных планшетов и др.

Чандрасехер уверен, что персональные мобильные устройства — основная движущая сила процесса дальнейшего распространения Интернета. С помощью подобных устройств мы сможем выходить на связь самыми разными способами и в самых разных местах.

«Сегодня исторический день для Intel и для всей высокотехнологичной отрасли — мы представили свои первые процессоры семейства Intel Atom с богатым набором поддерживаемых ими технологий. Благодаря уникальным инновациям наших партнеров — изготовителей устройств и разработчиков программного обеспечения — потребители получат совершенно новые возможности для доступа во Всемирную паутину и получения информации. Готовящиеся к выпуску MID-устройства, а также грандиозные долгосрочные планы заказчиков, которыми они поделились с нами, говорят о том, что маленькие устройства способны обеспечить большие интернет-возможности», — заявил г-н Чандрасехер.

На форуме IDF 2008 Ананд Чандрасехер официально представил процессоры Intel Atom (ранее известные под кодовым наименованием Silverthorne) и процессорную технологию Intel Centrino Atom — энергоэффективную платформу первого поколения для MID-устройств, которые могут поместиться в кармане, но при этом позволяют использовать все возможности Глобальной сети. Процессорная технология Intel Centrino Atom, ранее известная под кодовым наименованием Menlow, включает первый процессор Intel Atom (Silverthorne) и системный контроллер-концентратор Intel System Controller Hub (Poulsbo) с интегрированным графическим адаптером. Эти компоненты с самого начала разрабатывались для сегмента MID.

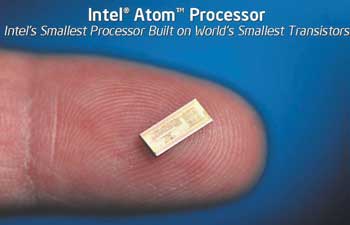

Процессор Intel Atom — это самый миниатюрный среди процессоров Intel. Площадь его кристалла составляет менее 25 мм2 (7,8x3,1 мм) и содержит более 47 млн транзисторов. Его архитектура разработана с нуля (то есть это не урезанный вариант процессора Penryn). Микроархитектура Intel Atom с самого начала разрабатывалась для того, чтобы достичь высокой производительности на ватт потребляемой мощности. Тепловыделение этого процессора составляет от 0,65 до 2,4 Вт, среднее энергопотребление — 160-220 мВт (милливатт), а энергопотребление в состоянии простоя — 80-100 мВт.

MID-устройство компании Lenovo на процессоре Intel Atom

При этом 32-битный процессор Intel Atom полностью совместим с набором инструкций IA-32 для процессоров семейства Intel Core 2 Duo (набор инструкций IA-64 не поддерживается) и поддерживает виртуализацию, технологию Hyper-Threading и расширение набора инструкций Digital Media Boost (SSE3). Безусловно, поддержка процессором виртуализации на аппаратном уровне кажется избыточной, если речь идет о MID-устройствах. Действительно, кому придет в голову устанавливать виртуальные машины и специализированное ПО на устройствах, предназначенных для решения совершенно иных задач? Однако, как будет показано в дальнейшем, процессоры Intel Atom могут использоваться не только в MID-устройствах, но и в устройствах, где поддержка виртуализации может оказаться отнюдь не лишней.

Новая микроархитектура основана на 45-нм производственном процессе, использующем новые транзисторы с металлическим затвором и диэлектриком high-k. В микроархитектуре Intel Atom реализованы революционные функции управления питанием, такие как состояние ожидания Intel Deep Power Down (C6), технология Enhanced Intel SpeedStep, активное стробирование генератора тактовых импульсов, режим CMOS и Split I/O. Все эти новшества позволяют оптимизировать энергопотребление и тепловыделение как в целом, так и в режимах ожидания, работы и пиковых нагрузок.

Размеры процессоров Intel Atom

Тактовая частота процессора Intel Atom достигает 1,86 ГГц, а частота FSB составляет 533 МГц (для младших моделей процессоров 400 МГц). При этом размер L2-кэша равен 512 Кбайт. Таким образом, данный процессор является самым быстродействующим среди процессоров с уровнем потребления энергии ниже 3 Вт, благодаря чему пользователи смогут быстро загружать веб-страницы и применять новейшие веб-технологии, такие как Adobe Flash и JavaScript.

Конечно, по сравнению с многоядерными процессорами технические характеристики одноядерного Intel Atom выглядят весьма скромно. Да и результаты первых тестов свидетельствуют о том, что его производительность лишь незначительно превосходит производительность процессора Intel Pentium III-M (Tualatin) c тактовой частотой 1,13 ГГц и уступает производительности процессора Intel Celeron M (Dothan) c тактовой частотой 900 МГц. Правда, в данном случае речь идет лишь об одном специфическом тесте вычисления числа p, однако, по всей видимости, и в других тестах ситуация будет примерно такой же. Естественно, об этом на форуме IDF не говорилось. В то же время процессоры Intel Atom предназначены в первую очередь для MID-устройств, которым высокая производительность просто не нужна, и в этом смысле не вполне корректно пользоваться традиционными тестами для определения их производительности. Для процессоров Intel Atom первостепенное значение имеет не производительность, а энергоэффективность — производительность в расчете на ватт потребляемой энергии, а по этому показателю новые процессоры действительно не имеют себе равных. Что же касается производительности как таковой, то тут более уместны иные критерии. Главное, чтобы эти процессоры справлялись с выполнением тех задач, на которые они ориентированы. Если говорить именно о MID-устройствах, то это прежде всего просмотр видео, прослушивание музыки, выход в Интернет и возможность эффективного веб-серфинга, общение через Интернет, в том числе с использованием встроенных веб-камер. Что касается возможностей этих процессоров в 3D-играх, то для этих целей они не предназначены. Более уместной в данном случае будет аналогия с процессорами типа PXA, используемыми в КПК. Мало кого из владельцев КПК интересует производительность установленного в них процессора. В конечном счете абсолютно неважно, какова тактовая частота процессора, к примеру PXA270. Даже если бы она составляла не 624, а 800 МГц или даже 1 ГГц, пользователь этого просто бы не заметил, поскольку с теми задачами, на которые ориентирован КПК, установленный в нем процессор успешно справляется, а более высокая производительность не будет востребована и лишь негативно скажется на времени автономной работы КПК. Точно так же и в случае MID-устройств — избыточная производительность процессора может оказаться невостребованной и лишь отрицательным образом отразится на энергопотреблении, а следовательно, и на времени автономной работы устройства.

Кристалл процессора Intel Atom

В общей сложности компания Intel представила пять различных процессоров Intel Atom (Z500, Z510, Z520, Z530 и Z540), разтличающихся тактовой частотой, частотой FSB, энергопотреблением и поддержкой технологии Hyper Threading (HT) — см. таблицу.

Системный контроллер-концентратор Intel System Controller Hub — это совершенно новое, высокоинтегрированное одночиповое решение с низким энергопотреблением, объединяющее в себе традиционные северный (GMCH) и южный (ICH) мосты чипсета.

Контроллер Intel SCH поддерживает частоту системной шины (FSB) 400 и 533 МГц, включает интегрированное графическое ядро Intel GMA 500, одноканальный контроллер памяти DDR2, звуковую подсистему Intel High Definition Audio, два порта PCI Express x1, восемь портов USB 2.0 в режиме хоста или семь портов USB в режиме хоста и один порт в режиме клиента, а также набор интерфейсов ввода-вывода (три порта SDIO/MMC) и контроллер PATA для подключения жестких дисков.

Контроллер памяти, интегрированный в чип Intel SCH, поддерживает только память DDR2-400 или DDR2-533 и позволяет адресовать максимально до 1 Гбайт памяти.

Интегрированное графическое ядро Intel GMA 500 обеспечивает API DirectX 9.0 (шейдерная модель 3.0+) и на аппаратном уровне поддерживает ускорение декодирования HD-видео в режимах 720p и 1080i (форматы H.264, MPEG-2, MPEG-4, VC1 и WMV9).

Кроме того, графическое ядро Intel GMA 500 включает два канала (LVDS и SDVO) для подключения мониторов. Канал LVDS (Low Voltage Differential Signaling) предназначен для подключения внутреннего ЖК-монитора, а канал SDVO (Serial Digital Video Out) — для подключения внешнего монитора.

Кроме того, процессорная технология Intel Centrino Atom позволит производителям устройств интегрировать в них целый ряд средств беспроводных коммуникаций, в том числе Wi-Fi, WiMAX и поддержку сотовых сетей.

Корпорация Intel представила три версии SCH (UL11L, US15L, US15W), поддерживающие различные операционные системы, модули памяти DDR2 400/533 МГц объемом 512 Мбайт и 1 Гбайт, видео как в стандартном разрешении, так и высокой четкости, технологии Intel High Definition Audio, DX9L и OpenGL.

Комплект компонентов на базе процессорной технологии Intel Centrino Atom, включающий системный контроллер-концентратор Intel System Controller Hub и процессор Intel Atom с частотой 800 МГц, 1,10, 1,33, 1,60 или 1,86 ГГц, стоит 45, 45, 65, 95 и 160 долл. соответственно (при заказе от 1000 штук).

Процессор Intel Atom и контроллер Intel SCH также будут использоваться в небольших безвентиляторных решениях для встраиваемых систем, таких как информационно-развлекательные системы в транспортных средствах, портативные устройства, устанавливаемые в кассовые терминалы на предприятиях розничной торговли, вычислительные устройства повышенной надежности (например, робототехника для промышленного производства). С июля станет доступным полный комплект программных драйверов для новой платформы. Теперь разработчики встраиваемых устройств смогут пополнить ассортимент своей продукции среднего и высшего класса, создавая более компактные системы без вентиляторов. Эта новая встраиваемая платформа на базе двух микросхем позволит более чем на 80% уменьшить размер устройств по сравнению с предыдущим решением, в котором было три микросхемы (процессор Intel Celeron M с ультранизким напряжением питания и набор микросхем Intel 945GME Express для мобильных ПК). Корпорация Intel также объявила о поддержке более 20 компаний, которые занимаются разработкой контроллеров для производственных автоматизированных систем. Компании Applied Data Systems и RadiSys также выпустили платформы с поддержкой процессоров Intel Atom, предназначенные для игровых устройств, контрольных и измерительных приборов, а также для военных и медицинских систем.

Итак, новое семейство процессоров Intel Atom может использоваться не только в принципиально новом классе мобильных интернет-устройств, но и в различных специализированных встраиваемых решениях. Впрочем, область возможного применения процессоров Intel Atom на практике оказывается еще шире и распространяется на такие устройства, как нетбуки (Netbook) и неттопы (Nettop).

От ноутбуков к нетбукам и неттопам

Новые термины — нетбук и неттоп — впервые прозвучали, конечно, не на весеннем форуме IDF 2008 в Шанхае, однако можно с уверенностью утверждать, что именно после него эти понятия прочно войдут в ИT-лексикон.

Первую публичную демонстрацию нетбуков на форуме IDF 2008 провел Дэвид Перлмуттер (David Perlmutter), старший вице-президент корпорации Intel и генеральный менеджер подразделения Mobility Group. Перлмуттер показал две концептуальные модели нетбуков на базе технологий Intel. Ожидается, что нетбуки на базе технологий Intel станут доступны уже в июне этого года.

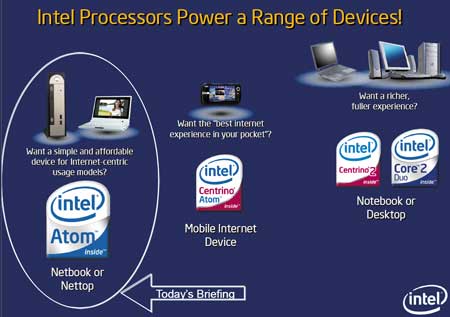

Итак, что же такое нетубки и неттопы и чем они отличаются от MID-устройств и традиционных ноутбуков?

Нетбуки и неттопы — это класс простых в эксплуатации и недорогих (сверхбюджетных) устройств, предназначенных для доступа в Интернет и ориентированных на решение таких задач, как веб-серфинг, просмотр видео, взаимодействие в социальных сетях и образование.

Позиционирование процессора Intel Atom

По сути, нетбуки — это вариант бюджетных сверхкомпактных ноутбуков начального уровня с размером дисплея от 7 до 10 дюймов по диагонали. Предполагается, что максимальная стоимость нетбуков не превысит планки в 400 долл. Через три года Intel рассчитывает ежегодно продавать до 40 млн комплектов для сборки нетбуков.

Естественно, что нетбуки существовали и ранее, но так не назывались. Классический пример подобного устройства — популярный и в каком-то смысле легендарный ASUS EeePC, а также Intel Classmate PC. Правда, следует отметить, что и ASUS EeePC, и Intel Classmate PC построены на несколько иной платформе, нежели та, которую предполагается применять в нетбуках, однако по своему назначению, стоимости и компактности ASUS EeePC и Intel Classmate PC как нельзя лучше соответствуют понятию нетбуков. В этом смысле можно сказать, что ASUS EeePC и Intel Classmate PC являются нетбуками первого поколения.

Сегмент нетбуков

Неттопы — это вариант сверхбюджетных настольных ПК стоимостью от 100 до 300 долл. В связи с этим нельзя говорить что-либо о размере экрана, поскольку неттопы предполагают использование внешнего монитора. Через три года Intel рассчитывает ежегодно продавать до 60 млн комплектов для сборки неттопов.

Интересно отметить, что и в нетбуках, и в неттопах предполагается применять операционную систему Linux или Windows XP. Естественно, что о ресурсоемкой Windows Vista в данном случае речи не идет.

Различные размеры процессора Intel Atom

Теперь обратимся к аппаратной конфигурации нетбуков и неттопов. Поскольку, как уже отмечалось, эти устройства ориентированы в первую очередь на работу в Интернете, то лучшим выбором для них, естественно, будет новый процессор Intel Atom. Правда, в данном случае речь идет не о процессорах Intel Atom серии Z5xx (кодовое название Silverthorne), а о процессорах с кодовым названием Diamondville. В отличие от процессоров серии Z5xx, которые имеют размер платы 13x14 мм (не путать с размером кристалла), процессоры Diamondville имеют размер 22x22 мм. Естественно, разъемы у процессоров Silverthorne и Diamondville различные. Все остальные характеристики у этих процессоров одинаковые. В частности, процессоры Diamondville выполнены по 45-нанометровому техпроцессу, являются одноядерными и имеют энергопотребление порядка 2 Вт, размер L2-кэша составляет 512 Кбайт, а частота FSB — 533 МГц. Поддерживается технология Hyper-Threading.

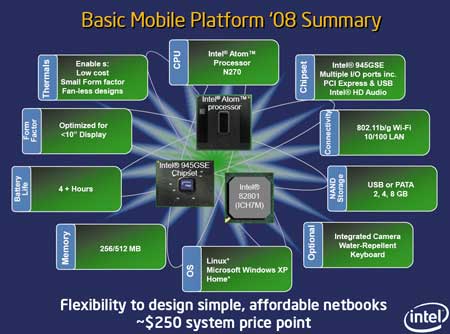

Платформа для нетбука

В дальнейшем ожидается, что линейка процессоров Intel Atom пополнится и двухъядерными вариантами, которые, естественно, будут иметь другие характеристики.

Итак, вернемся к аппаратной конфигурации нетбуков. Первоначально платформа нетбуков будет включать процессор Intel Atom N270 (Diamondville) с тактовой частотой 1,66 ГГц, который выйдет в июне этого года. Платформа нетбуков будет включать также чипсет Intel 945 GSE (южный мост ICH7M) со встроенным графическим контроллером. Нетбуки будут оснащаться 256 или 512 Мбайт оперативной памяти DDR2, использовать 2-, 4- или 8-гигабайтные флэш-диски на основе NAND-памяти (возможно также использование традиционных HDD-дисков с PATA-интерфейсом). Кроме того, опционально неттопы могут оснащаться встроенной веб-камерой, а коммуникационные возможности неттопов предполагают наличие интегрированного сетевого адаптера Ethernet и беспроводного адаптера Wi-Fi c поддержкой беспроводного стандарта 802.11b/g. Предположительное время автономной работы неттопов составит более 4 ч.

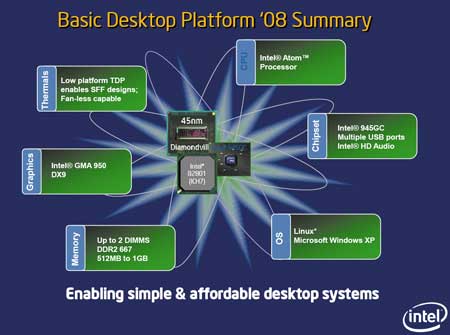

Платформа для неттопа

Что касается аппаратной конфигурации неттопов, то пока компания Intel точно не называет модели процессора семейства Intel Atom, который будет в них использоваться. Известно лишь, что это будет процессор c кодовым названием Diamondville. По неофициальным данным, в первых моделях неттопов будет установлен процессор Intel Atom 230 (официально этот процессор еще не объявлен) с тактовой частотой 1,6 ГГц. Вариант настольного процессора Intel Atom 230 будет отличаться несколько большим тепловыделением (порядка 4 Вт), что, однако, все равно позволит создавать компьютеры с пассивной системой охлаждения. Стоить этот процессор будет всего 29 долл.

Материнская плата для неттопа

В неттопах будет применяться чипсет Intel 945GC (южный мост ICH7) с интегрированным графическим контроллером Intel GMA 950. Неттопы будут оснащаться памятью DDR2-667 объемом 512 Мбайт или 1 Гбайт (на системных платах неттопов для установки модулей памяти предусматривается два DIMM-слота). Еще раз напомним, что, как и в нетбуках, в неттопах будет использоваться операционная система Linux или Windows XP.

Ультрамобильная платформа следующего поколения Moorestown

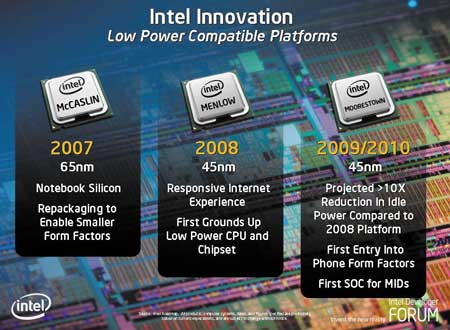

Естественно, что в рамках форума IDF 2008 немало внимания было уделено и будущим мобильным платформам. В частности, Чандрасехер рассказал о мобильной платформе следующего поколения с кодовым наименованием Moorestown, начало выпуска которой намечено на 2009-2010 годы. Правда, пока об этой плафторме известно немного (по словам Чандрасехера, подробности о ней можно будет узнать на осеннем форуме IDF 2008 в Тайпее), но даже скудная информация — это лучше, чем ничего.

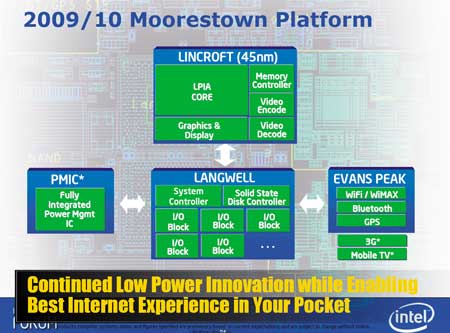

Итак, известно, что в платформе Moorestown будет реализована идея системы на одном кристалле (System-on-Chip, SoC).

Платформа Moorestown включает однокристальный чип Lincroft и контроллер-концентратор ввода-вывода Langwell.

Платформы Moorestown

Однокристальный чип Lincroft объединяет 45-нм процессор Silverthorne, графический контроллер и контроллер памяти.

Развитие ультрамобильных платформ

Контроллер-концентратор ввода-вывода Langwell будет поддерживать ряд технологий ввода-вывода, в том числе интерфейсы памяти и дисплея, а также сможет взаимодействовать с устройствами управления питанием (PMIC) и беспроводными решениями сторонних производителей.

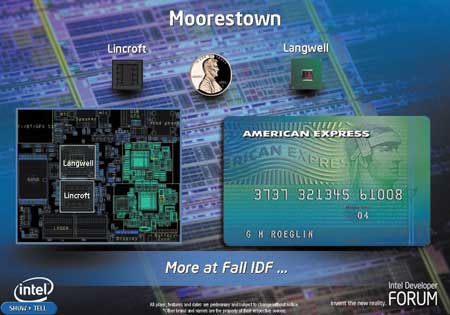

Размер материнской платы в платформе Moorestown

В рамках форума IDF 2008 Чандрасехер продемонстрировал самую маленькую в мире системную плату для платформы Moorestown — ее размер сопоставим с размером кредитной карточки.

Примечательно, что платформу Moorestown планируется использовать не только в MID-устройствах, но и в смартфонах, в связи с чем появились слухи, что следующее поколение легендарных iPhone будет основано на платформе Moorestown. Тем не менее еще раз подчеркнем, что эта информация не имеет официального подтверждения. Однако то, что с выходом платформы Moorestown Intel попытается покорить рынок смартфонов, — факт бесспорный.

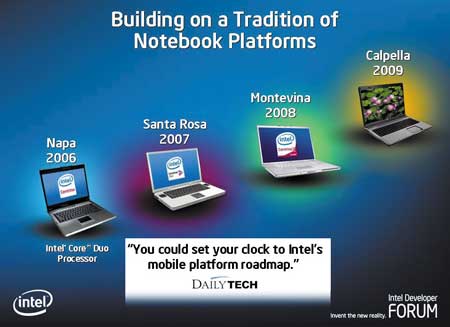

Montevina и Calpella — платформы для ноутбуков следующего поколения

Несмотря на то что тема процессоров Intel Atom и новой платформы для MID-устройств стала центральной на форуме, немало внимания было уделено и дальнейшему развитию платформ для ноутбуков. Все-таки MID-устройства и нетбуки — это хорошо, но ноутбуки еще никто не отменял, и, естественно, компания Intel, которая уже давно и прочно удерживает позиции лидера в сегменте ноутбуков, просто не могла обойти вниманием эти вопросы.

Описывая новейшие тенденции в области мобильной вычислительной техники, Дэвид Перлмуттер, старший вице-президент и генеральный менеджер подразделения Mobility Group корпорации Intel, особое внимание уделил будущим платформам Intel для ноутбуков.

Дэвид Перлмуттер рассказал о мобильной платформе нового поколения под кодовым названием Montevina, выпуск которой планируется начать в июне текущего года. Эта платформа станет основой процессорной технологии Intel Centrino 2.

В мобильную платформу Montevina включены 45-нм процессор семейства Penryn и набор микросхем нового поколения Cantiga, поддерживающий память DDR3. Кроме того, в этой платформе будет реализована технология Robson 2.0 (следующая версия технологии Intel Turbo Memory).

Процессорная технология Intel Centrino 2 станет первой платформой Intel, в которую будет включен опциональный интегрированный модуль Echo Peak, поддерживающий технологии Wi-Fi и WiMAX для расширения полосы пропускания беспроводных коммуникаций.

Размер платформ для ноутбуков

Решение Echo Peak содержит передовую технологию антенн MIMO, позволяющую увеличить пропускную способность канала данных и расширить возможности широкополосного доступа для пользователей — дома, на работе и в пути. Интеграция стандартов Wi-Fi и WiMAX в данную платформу позволит не только высвободить столь ценную площадь внутри мобильного ПК для других целей, но и создать очень экономичное решение, обеспечить высокую скорость подключения устройств и значительное сокращение расходов. Правда, модели ноутбуков, оснащенные модулем Echo Peak, появятся не раньше 2009 года, но, естественно, г-н Перлмуттер упомянуть об этом в своем докладе забыл.

Кроме того, платформа Montevina будет поддерживать видеоформат Blu-ray (для индивидуальных пользователей), а также новое поколение средств управления данными и функций обеспечения информационной безопасности (для бизнес-пользователей). Перлмуттер сообщил, что Intel разрабатывает технологию Intel Anti-theft Technology, которая дополнит и усовершенствует решения по информационной безопасности, предлагаемые сегодня ведущими производителями компьютеров и программного обеспечения. Эта технология, сфокусированная на восстановлении ресурсов, предотвращении краж и защите данных, появится в ноутбуках до конца текущего года.

Вслед за мобильной платформой Montevina в 2009 году будет выпущена платформа с кодовым названием Calpella. Правда, пока об этой новой платформе никаких подробностей не сообщается. Фактически, все, что известно, — это кодовое название платформы и то, что она будет включать процессор на базе микроархитектры Nehalem с интегрированным контроллером памяти DDR3. Учитывая, что процессоры на базе микроархитектуры Nehalem будут выполняться как с интегрированным графическим контроллером, так и без него, можно предположить, что в сегменте корпоративных и бюджетных ноутбуков будут существовать решения с интегрированным в процессор графическим ядром, а в сегменте домашних и игровых ноутбуков — решения с дискретной графикой (причем, возможно, с дискретной графикой от самой компании Intel). Можно также предположить, что, поскольку компания Intel выходит на рынок SSD-дисков и уже анонсировала свои продукты емкостью от 32 до 160 Гбайт, в платформе Montevina будут использоваться преимущественно твердотельные диски.

Микроархитектура Nehalem

Естественно, на форуме IDF 2008 обсуждались и очередные подробности, касающиеся новой процессорной микроархитектуры Nehalem. Почему очередные подробности? Дело в том, что о новой процессорной микроархитектуре Nehalem говорят уже не первый год. И на каждом форуме IDF компания Intel выдает о ней все больше и больше подробностей. Так, первоначально было известно лишь кодовое название новой микроархитектуры. Затем, на осеннем форуме IDF 2007, была проведена первая публичная демонстрация процессора под кодовым наименованием Nehalem, однако никаких подробностей не сообщалось. Было известно лишь, что на базе микроархитектуры Nehalem будут производиться 2-, 4- и 8-ядерные процессоры, причем каждое ядро процессора будет поддерживать одновременную многопоточную обработку данных (аналогично технологии Intel Hyper-Threading). Таким образом, с точки зрения операционной системы каждое ядро процессора будет представляться как два отдельных ядра. Также было известно, что главной особенностью микроархитектуры Nehalem станет интегрированный в процессор контроллер памяти, а также архитектура QuickPath Interconnect, позволяющая связывать процессоры между собой и с остальными компонентами системы. Ну и последнее, что было известно, — это то, что процессоры Nehalem опционально могут содержать интегрированный графический контроллер. Правда, никаких деталей относительно того, будет ли это отдельный графический контроллер, интегрированный внутрь упаковки процессора, или функции графического контроллера будут выполнять несколько ядер процессора, на осеннем форуме IDF 2007 не сообщалось.

Теперь настало время ликвидировать все пробелы и поговорить о новой микроархитектуре более подробно. В первую очередь сообщим самые общие сведения.

В своем выступлении на форуме IDF Патрик Гелсингер (Pat Gelsinger), старший вице-президент Intel и генеральный менеджер подразделения Digital Enterprise Group, привел некоторые технические данные следующего поколения процессоров с микроархитектурой под кодовым названием Nehalem, производство которых начнется в IV квартале. Сначала процессоры Nehalem появятся в сегменте высокопроизводительных настольных ПК и двухпроцессорных серверных систем, в других сегментах рынка они будут представлены в 2009 году. Конструктивно процессоры Nehalem способны масштабироваться от двух до восьми ядер. Гелсингер сообщил о новом наборе инструкций Intel Advanced Vector Extension, поддержка которого планируется с 2010 года в следующем после Nehalem семействе процессоров с кодовым названием Sandy Bridge.

Кроме того, на форуме IDF 2008 были продемонстрированы рабочие образцы новых процессоров на базе микроархитектуры Nehalem. Речь идет о четырехъядерном процессоре с кодовым названием Bloomfield. Этот процессор, ориентированный на высокопроизводительные компьютеры, появится одним из первых в семействе процессоров на базе архитектуры Nehalem. Он будет изготавливаться по 45-нанометровой технологии, а его TDP составит 130 Вт.

Также известно, что процессоры на базе микроархитектуры Nehalem будут иметь новый разъем. В частности, четырехъядерные процессоры для настольных систем (Bloomfield) будут оснащены разъемом LGA1366, то есть будут иметь 1366 контактов. Размер упаковки процессора составит 42,5x45 мм (размер упаковки процессора с разъемом LGA775 —37,5x37,5 мм).

Далее мы более детально рассмотрим новую микроархитектуру Nehalem на примере четырехъядерного процессора Bloomfield.

Процессор Bloomfield

Данный процессор содержит четыре ядра на одном кристалле (то есть является подлинно четырехъядерным) и поддерживает технологию Simultaneous Multi-Threading (SMT). Данная технология является аналогом технологии многопоточной обработки данных Hyper-Threading, известной еще по процессорам Intel Pentium 4 с архитектурой NetBurst. Следовательно, технология SMT позволяет каждому ядру процессора одновременно обрабатывать два отдельных потока, поэтому каждое физическое ядро процессора с точки зрения операционной системы видится как два отдельных логических процессора, а весь четырехъядерный процессор Bloomfield — как восемь отдельных процессоров.

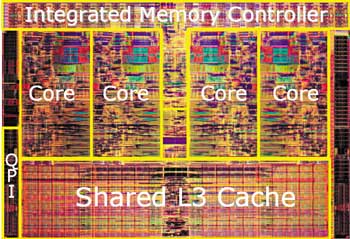

Кристалл процессора Bloomfield

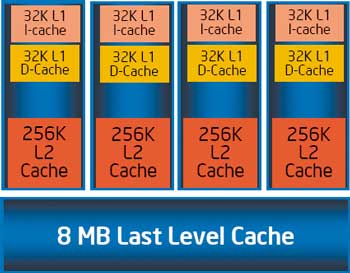

Следующая особенность процессора Bloomfield, как и всех процессоров семейства Nehalem, заключается в том, что контроллер памяти интегрирован в сам процессор. Причем в процессорах Nehalem будет применяться уже трехканальный контроллер памяти (Integrated Memory Controller, IMC) DDR3. Попутно заметим, что интегрированный контроллер памяти поддерживает память DDR3 800, 1066 и 1333 и использование до двух DIMM-слотов на каждый канал.

Еще одна особенность процессора Bloomfield заключается в том, что на кристалле процессора расположен разделяемый между всеми ядрами L3-кэш размером 8 Мбайт. Напомним, что в процессорах с архитектурой Intel Core применяется разделяемый между всеми ядрами кэш L2. В процессорах с архитектурой Nehalem кэш L2 не является разделяемым и находится в эксклюзивном использовании каждого ядра процессора, однако при этом предусмотрен разделяемый кэш L3.

Структура кэша в процессоре Bloomfield

В процессоре Bloomfield каждому его ядру отводится кэш L2 размером 256 Кбайт.

Последняя особенность процессоров на базе микроархитектуры Nehalem — это то, что вместо шины FSB, которая ранее служила для связи процессора с чипсетом, теперь применяется принципиально иной интерфейс, называемый Intel QuickPath Interconnect (QPI). Соответственно на кристалле процессора расположен также контроллер шины QPI. Шина QPI служит для связи процессора с чипсетом и для связи процессоров друг с другом (в случае многопроцессорных конфигураций).

Структура шины QPI

QPI является последовательной, высокоскоростной двунаправленной шиной. Ее ширина в каждую сторону (передача и прием) составляет по 20 бит (20 отдельных пар линий), при этом 16 бит отводится для передачи данных, две линии зарезервированы для передачи служебных сигналов и еще две — для передачи кодов коррекции ошибок CRC. C учетом еще двух пар линий, используемых для синхронизации сигналов (одна на прием и одна на передачу), получаем, что шина QPI состоит из 42 пар линий, то есть является 84-контактной.

Пропускная способность шины QPI составляет 25,6 Гбайт/с.

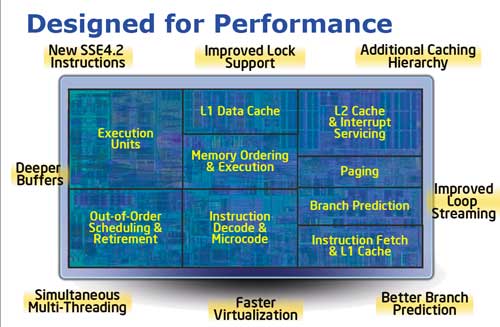

Ядро процессора на базе микроархитектуры Nehalem

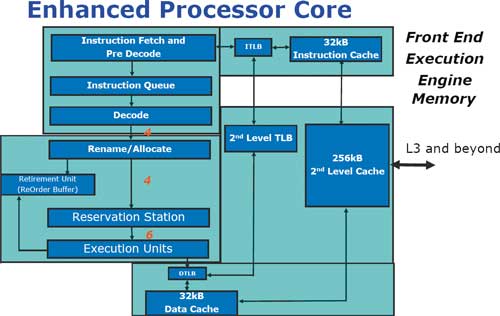

После рассмотрения в общих чертах структуры процессора Bloomfield более детально ознакомимся с особенностями ядра процессора на базе микроархитектуры Nehalem. Но прежде нам предстоит освежить в памяти основные принципы работы процессоров, функционирующих по конструктивной схеме простейшего гипотетического процессора.

Напомним, что в основе архитектуры любого процессора имеется несколько конструктивных элементов: кэш команд и данных, предпроцессор (Front End) и постпроцессор, который также называется блоком исполнения команд (Execution Engine).

Процесс обработки данных состоит из нескольких характерных этапов. Сначала программные инструкции выбираются из кэша инструкций процессора. Эта процедура называется выборкой. Затем выбранные из кэша инструкции декодируются в понятные для данного процессора примитивы (машинные команды). Далее декодированные команды поступают на исполнительные блоки процессора и выполняются, а результат записывается в оперативную память.

Процесс выборки инструкций из кэша, их декодирование и продвижение к исполнительным блокам осуществляются в предпроцессоре, а процесс выполнения декодированных команд — в постпроцессоре. Таким образом, даже в простейшем случае команда проходит как минимум четыре стадии обработки, которые принято называть конвейером обработки команд. В нашем гипотетическом случае конвейер является четырехступенчатым. Важно, что каждую из этих ступеней команда должна проходить ровно за один такт. Соответственно для четырехступенчатого конвейера на выполнение одной команды отводится ровно четыре такта.

Размещение функциональных блоков на кристалле ядра процессора

Еще раз отметим, что рассмотренный нами процессор является гипотетическим. В реальных процессорах конвейер обработки команд может быть более сложным и включать большее число ступеней. Однако сама идеология построения процессора остается неизменной. Причина увеличения длины конвейера заключается в том, что многие команды являются довольно сложными и не могут быть выполнены за один такт процессора, особенно при высоких тактовых частотах. Поэтому каждая из четырех стадий обработки команд (выборка, декодирование, выполнение и запись) может состоять из нескольких ступеней конвейера.

Теперь перейдем к рассмотрению микроархитектуры Nehalem.

Микроархитектура Nehalem

Новая микроархитектура Nehalem во многом напоминает микроархитектуру Intel Core, но по сравнению с ней имеет ряд улучшений.

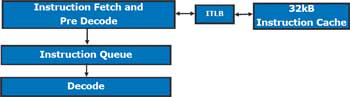

Начнем с блока предпроцессора, который отвечает за выборку инструкций из кэша, их декодирование и предсказание программных переходов.

При работе процессора инструкции x86 выбираются из кэша инструкций L1 (Instruction Сache) размером 32 Кбайт. Команды загружают из кэша блоками фиксированной длины, из которых выделяются инструкции, направляемые на декодирование. Поскольку инструкции x86 имеют переменную длину, а блоки, которыми команды загружаются из кэша, — фиксированную, при декодировании команд нужно определить границы между отдельными командами.

Информация о размерах команд хранится в кэше инструкций L1 в специальных полях (по 3 бита информации на каждый байт инструкций). В принципе, эту информацию для определения границ команд можно было бы применять в самом декодере непосредственно в процессе декодирования команд. Однако это неизбежно отразилось бы на скорости декодирования, да и декодировать одновременно несколько команд невозможно. Поэтому перед декодированием производится выделение команд из выбранного блока — предварительное декодирование (PreDecode). Процедура предварительного декодирования позволяет поддерживать постоянный темп декодирования независимо от длины и структуры команд.

Структурная схема предпроцессора в архитектуре Nehalem

Процессоры с архитектурой Intel Core производят выборку команд 16-байтными блоками, то есть за каждый такт из кэша загружается 16-байтный блок команд. Какова длина блока выборки команд в архитектуре Nehalem, в материалах форума IDF 2008 нам обнаружить не удалось, однако можно предположить, что она также составляет 16 байт. На эту мысль наводит тот факт, что в архитектуре Nehalem используется точно такой же четырехканальный декодер, как и в архитектуре Intel Core. Впрочем, об этом чуть позже.

Далее команды организуются в очередь (Instruction Queue), а затем передаются в декодер. При декодировании (Decode) команды преобразуются в машинные микрооперации (micro-op).

После процесса декодирования команд начинается этап их исполнения. Первоначально происходит переименование и распределение дополнительных регистров процессора (Allocate & Rename), которые не определены архитектурой набора команд. Переименование регистров позволяет добиться исполнения команд вне очереди. Идея переименования регистров заключается в следующем. В архитектуре x86 количество регистров общего назначения сравнительно невелико — доступно восемь регистров в 32-битном режиме, и 16 — в 64-битном. Представим, что исполняемая команда дожидается загрузки значений операндов в регистр из памяти. Это долгая операция, и хорошо бы на это время позволить применять этот регистр для другой команды, операнды которой находятся ближе (например, в кэше первого уровня). Для этого временно переименовывается «ждущий» регистр и отслеживается история переименования; «готовому к работе» регистру присваивается стандартное имя, чтобы снабженную операндами команду исполнить прямо сейчас, а когда придут данные из памяти, обращаются к истории переименования и возвращают изначальному регистру его законное имя. Иными словами, техника переименования регистров позволяет снизить простои, а ведение истории переименования используется для нивелирования конфликтов.

На следующем этапе (буфер переупорядочения (ReOrder Buffer)) происходит переупорядочение микроопераций не в порядке их поступления (Out-of-Order) с тем, чтобы впоследствии можно было реализовать их более эффективное выполнение на исполнительных блоках. Отметим, что буфер переупорядочения ReOrder Buffer и блок отставки (Retirement Unit) совмещены в едином блоке процессора, но первоначально производится переупорядочение инструкций, а блок Retirement Unit включается в работу позже, когда надо выдать исполненные инструкции в заданном программой порядке.

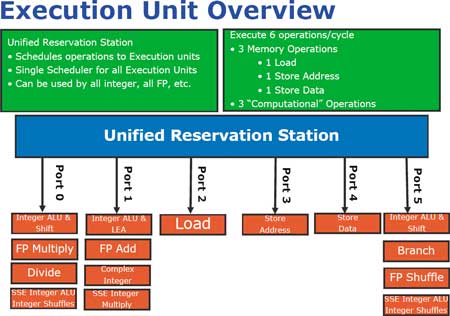

Далее происходит распределение микроопераций по исполнительным блокам. В блоке процессора Reservation Station формирует очереди микроопераций, в результате чего микрооперации попадают на один из портов функциональных устройств (dispatch ports). Этот процесс называется диспетчеризацией (Dispatch), а сами порты выполняют функцию шлюза к функциональным устройствам.

После того как микрооперации пройдут порты диспетчеризации, они направляются в соответствующие функциональные блоки для дальнейшего выполнения.

Собственно, в описанной схеме нет ничего принципиально нового в сравнении с архитектурой Intel Core. Да это и понятно, поскольку описанная нами схема является общей и справедлива для процессоров с любой архитектурой. Однако, отличия в сравнении с архитектурой Intel Core все же имеются, причем весьма значительные. Напомним, что одной из особенностей архитектуры Intel Core была совокупность технологий, получивших обобщающее название Intel Wide Dynamic Execution. К наиболее важным технологиям из набора Intel Wide Dynamic Execution относятся следующие:

- механизм декодирования до четырех инструкций за такт;

- технология слияния макроопераций MacroFusion;

- технология слияния микроопераций micro-ops fusion.

- Intel Wide Dynamic Execution используется и в архитектуре Nehalem, но в данном случае речь идет об усовершенствованной технологии.

Блок декодирования

По сравнению с ядрами процессоров семейства Pentium M и Pentium 4, где за каждый такт могло декодироваться до трех программных инструкций, декодер ядра процессора с архитектурой Intel Core является четырехканальным и может декодировать в каждом такте до четырех инструкций x86. Напомним, что за каждый такт из кэша загружается 16-байтный блок команд, из которого в процессе предварительного декодирования выделяются отдельные команды. В принципе, длина одной команды может достигать 16 байт. Однако средняя длина команд составляет 4 байта. Поэтому в среднем в каждом блоке загружается четыре команды, которые в случае применения четырехканального декодера одновременно декодируются за один такт.

В архитектуре Nehalem декодер также является 4-канальным и способен декодировать в каждом такте до четырех инструкций x86. Именно поэтому мы и предположили, что в архитектуре Nehalem команды также загружаются 16-байтными блоками.

Отметим, что в архитектуре Nehalem, как и в Intel Core, четырехканальный декодер состоит из трех простых декодеров, которые декодируют простые инструкции в одну микрооперацию, и одного сложного, который способен декодировать одну инструкцию в четыре микрооперации (декодер типа 4-1-1-1). Для еще более сложных инструкций, которые декодируются более чем в четыре микрооперации, сложный декодер соединен с блоком uCode Sequenser, который и используется для декодирования подобных инструкций.

Естественно, что декодирование четырех инструкций за такт возможно только в том случае, если в одном 16-байтном блоке содержится не менее четырех инструкций. Однако существуют команды и длиннее 4 байт, и при загрузке нескольких таких команд в одном блоке эффективность декодирования снижается.

Слияние микроопераций

Технология MacroFusion, впервые реализованная в архитектуре Intel Core, основана на слиянии двух инструкций x86 в одну. В предыдущих версиях процессорной микроархитектуры каждая инструкция в формате x86 декодировалась независимо от остальных. При применении технологии Macro Fusion некоторые пары инструкций (например, инструкция сравнения и условного перехода) при декодировании могут быть слиты в одну микроинструкцию (micro-op), которая в дальнейшем будет выполняться именно как одна микроинструкция. Отметим, что для эффективного поддержания технологии Macro Fusion в архитектуре Intel Core использовались расширенные блоки ALU (Arithmetical Logic Unit), которые способны поддержать выполнение слитых микроинструкций. Отметим также, что без применения технологии MacroFusion за каждый такт процессора могло декодироваться только четыре инструкции (в четырехканальном декодере). При использовании технологии MacroFusion в каждом такте могло считываться пять инструкций, которые преобразуются в четыре за счет слияния и подвергаются декодированию.

В архитектуре Nehalem технология MacroFusion получила дальнейшее усовершенствование. В частности, расширен набор команд, для которых возможно слияние. Кроме того, если в архитектуре Intel Core технология MacroFusion реализовывалась только в 32-битном режиме работы процессора, то в архитектуре Nehalem данная технология реализуется и в 64-битном режиме.

Технология micro-ops fusion

Технология слияния микроопераций micro-ops fusion, которая имелась еще в архитектуре Intel Core, заключается в том, что в ряде случаев две микрооперации сливаются в одну операцию, содержащую два элементарных действия. В дальнейшем две такие слитые микрооперации обрабатываются как одна, что в результате позволяет снизить количество обрабатываемых микроопераций и тем самым увеличить общее число исполняемых процессором инструкций за один такт. В архитектуре Nehalem также используется технология слияния микроопераций, однако ни о каких отличиях данной технологии от технологии micro-ops fusion в архитектуре Intel Core не сообщается.

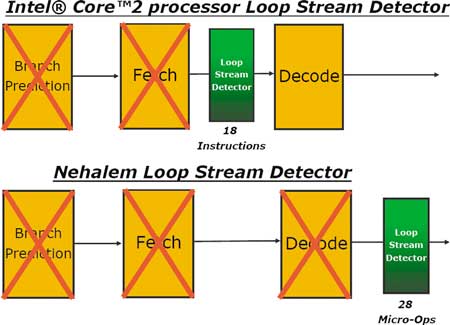

Технология Loop Stream Detector

Loop Stream Detector — это технология обнаружения программных циклов. В любом программном коде практически всегда присутствуют программные циклы, в результате выполнения которых процессору приходится декодировать одни и те же инструкции. Дабы избежать выполнения одних и тех же операций (предсказания ветвлений, выборки) в процессорах с архитектурой Intel Core применяется блок обнаружения циклов (Loop Stream Detector). В архитектуре Intel Core использовался буфер Loop Stream Detector на 18 инструкций, причем сам буфер располагался перед декодером. То есть в архитектуре Intel Core могли отслеживаться и распознаваться только циклы, содержащие не более 18 инструкций. При обнаружении программного цикла инструкции в цикле пропускают фазы выборки и предсказания ветвлений в программе, а сами команды генерируются и поступают в декодер непосредственно из Loop Stream Detector. С одной стороны, это позволяет снизить энергопотребление ядра процессора, а с другой — обойти фазу выборки команд. В случае если в цикле насчитывается более 18 инструкций, то каждый раз инструкции будут проходить все стандартные шаги.

Технология Loop Stream Detector

В архитектуре Nehalem используется улучшенный блок обнаружения циклов. Изменения коснулись его расположения. Теперь он находится за декодером и рассчитан на 28 декодированных инструкций, что позволяет обнаруживать циклы на 60% более длинные. Кроме того, поскольку Loop Stream Detector хранит декодированные инструкции (поскольку расположен после декодера), инструкции будут «пропускать» не только фазу предсказания ветвлений и выборки, как раньше, но и фазу декодирования. Таким образом, в Nehalem инструкции в цикле будут проходить через конвейер быстрее и чаще.

Новый двухуровневый TLB-буфер

Еще одно важное нововведение в архитектуре Nehalem — это использование двухуровневой иерархии буфера ассоциативной трансляции (Translation Lookaside Buffer, TLB), или буфера трансляции виртуальных адресов страниц памяти в физические.

То есть если традиционно в архитектуре Intel Core использовались два отдельных TLB-буфера для инструкции (ITLB) и данных (DTLB), которые можно рассматривать как буферы первого уровня, то теперь дополнительно введен унифицированный TLB-буфер для данных и команд, который является буфером второго уровня. TLB-буфер второго уровня рассчитан на 512 записей, причем поддерживаются записи только для страниц памяти размером 4K (Small Page). При этом ITLB-буфер рассчитан на 128 записей страниц памяти типа Small Page и семь записей (в расчете на один поток) для страниц типа Large Page (размером 2M/4M). Буфер DTLB рассчитан на 64 записи страниц памяти типа Small Page и 32 записи для страниц типа Large Page.

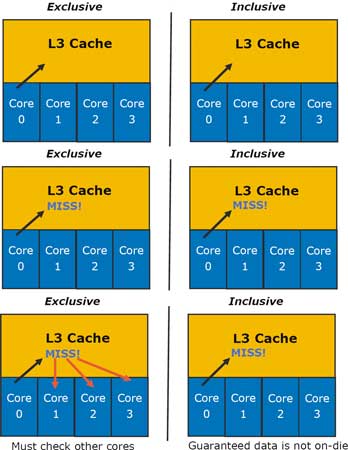

Кэши L1, L2 и L3

Как мы уже отмечали, одна из главных особенностей новой архитектуры — это изменение структуры кэш-памяти процессора. Собственно, кэш-память первого уровня (L1) не претерпела изменений (изменился лишь размер TLB-буфера): 32 Kбайт отводится для кэша данных и 32 Kбайт — для кэша инструкций. Кэш L1 является 8-канальным, а размер строки кэша равен 64 байт.

Новизна заключается в том, что к каждому ядру процессора теперь добавлен унифицированный (единый для инструкций и данных) кэш второго уровня (L2) размером 256 Кбайт, и разделяемый между всеми ядрами процессора кэш третьего уровня (L3).

Кэш L2, так же как и L1, является 8-канальным, а размер строки кэша составляет 64 байт.

Размер разделяемого кэша L3 может быть различным и зависит от числа ядер процессора. В частности, как мы уже отмечали, для четырехъядерного процессора Bloomfield размер L3-кэша составляет 8 Мбайт.

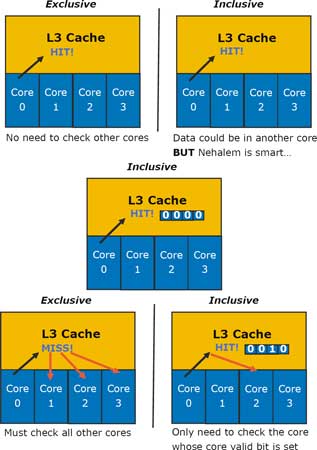

Кэш L3 является включающим (inclusive) по своей архитектуре по отношению к кэшам L1 и L2, то есть в кэше L3 всегда дублируется содержимое кэшей L1 и L2. Отметим, что кэши L1 и L2 не являются ни включающими, ни исключающими по отношению друг к другу.

Кэш L3 тоже 16-канальный и имеет размер строки 64 байт.

Преимущество включающего кэша в сравнении

с исключающим

в случае отсутствия данных в кэше L3

Использование именно включающего кэша L3 имеет свои преимущества по сравнению с исключающей архитектурой. Рассмотрим несколько характерных примеров чтения данных из кэша L3. Предположим сначала, что ядро процессора Core 0, обнаружив, что требуемых ему данных нет ни в кэше L1, ни в кэше L2, обращается к кэшу L3. Если требуемых данных нет и в кэше L3, то в случае исключающей архитектуры кэша L3 потребовалось бы также проверить наличие требуемых данных в кэшах L1 и L2 каждого из ядер Core 1, Core 2 и Core 3. В случае включающей архитектуры кэша L3 необходимость в подобной проверке пропадает, поскольку включающая архитектура кэша L3 гарантирует, что при отсутствии данных в кэше L3 они будут отсутствовать и в кэше L1 и L2.

Преимущество включающего кэша в сравнении

с исключающим

в случае наличия данных в кэше L3

Если же требуемые ядру Core 0 обнаруживаются в кэше L3, то при исключающей архитектуре кэша более не требуется предпринимать каких-либо действий, поскольку данная архитектура гарантирует их отсутствие в кэшах L1 и L2 ядер Core1, Core 2 и Core 3. Однако при включающей архитектуре кэша L3 наличие требуемых данных в кэше L3 означает, что они также содержатся и в каком-то из кэшей ядра Core 1, Core 2 или Core 3. Для того чтобы определить, в кэш-памяти какого именно ядра находятся данные, в тэг-поле кэш-строки L3-кэша записывается, к какому из ядер принадлежат данные.

Другие изменения архитектуры

Естественно, что описанными изменениями в архитектуре Nehalem в сравнении с архитектурой Intel Core дело не ограничивается. Так, увеличен размер буфера переупорядочения (ReOrder Buffer, ROB) — если ранее он был рассчитан на 98 микроинструкций, то теперь в нем можно размещать 128 микроинструкций. Кроме того, существенно улучшен механизм предсказания ветвлений.

Подверглись переработке и исполнительные блоки ядра процессора. Процессор на базе микроархитектуры Nehalem способен выполнять до шести операций за такт. При этом возможно выполнение одновременно трех вычислительных операций и трех операций с памятью.

Исполнительные блоки в процессоре на базе микроархитектуры Nehalem

Еще одно существенное нововведение — это новый набор расширений инструкций SSE4.2. Он включает поддержку всех 47 команд SSE4, а также семи новых программно-ориентированных ускорителей (Application Targeted Accelerator, ATA) обработки строк и текстовой информации. По утверждению разработчиков, дополнительные ускорители будут полезны, например, в задачах лексического и синтаксического анализа, при работе с регулярными выражениями и поиске вирусов.

Заключение

Конечно, рассмотренные в нашей статье вопросы не исчерпывают весь спектр вопросов форума IDF 2008. К примеру, за рамками нашего рассмотрения остались новинки серверного рынка, шестиядерный процессор Dunnington и многое другое. Естественно, к теме IDF 2008 мы так или иначе будем еще неоднократно возвращаться в своих статьях.