Компания Intel начинает массовое производство трехмерных транзисторов Tri-Gate

4 мая компания Intel объявила о выходе на новый виток в эволюции транзисторов. Впервые за их 50-летнюю историю в массовом производстве будет применена трехмерная структура. Новую технологию Tri-Gate, разработанную Intel, планируется внедрить до конца текущего года при выпуске процессоров под кодовым наименованием Ivy Bridge. Новые чипы будут производиться на основе 22-нанометровой технологии.

Немного истории

Как известно, транзисторы — это микроскопические кремниевые «переключатели», которые являются основным структурным элементом всех современных микросхем.

Первый транзистор был создан 16 декабря 1947 года в лаборатории Bell Labs американцами Уильямом Шокли, Уолтером Браттейном и Джоном Бардином. Это был первый биполярный транзистор.

18 октября 1954 года был создан и стал массово производиться первый транзисторный радиоприемник Regency TR1, в котором насчитывалось четыре биполярных транзистора. А уже 25 апреля 1961 года Роберт Нойс получил патент на изобретение первой интегральной микросхемы, содержащей несколько планарных полевых транзисторов. Кстати, позднее, в 1968 году, Нойс и его давний коллега Гордон Мур основали корпорацию Intel.

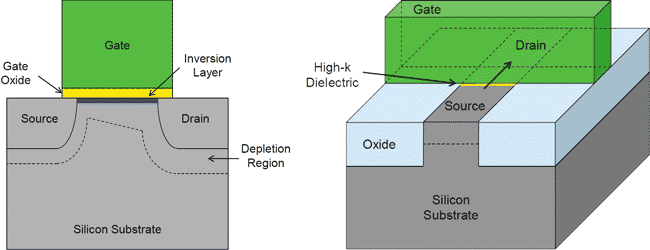

Начиная с 60-х годов, то есть со времени создания первой микросхемы, и по сей день в микросхемах используются именно планарные полевые транзисторы. Принцип действия такого транзистора довольно прост (рис. 1).

Рис. 1. Схема планарного транзистора

В подложке кремния (Silicon Substrate) формируются две легированные области с электронной (n-тип) или дырочной (p-тип) проводимостью. Эти области называются стоком (Drain) и истоком (Source). В обычном состоянии электроны (для n-типа) или дырки (для p-типа) хотя и диффундируют в область кремния за счет избыточной концентрации, но не способны перемещаться между стоком и истоком, поскольку неизбежны процессы рекомбинации в области кремния. Кроме того, за счет такой диффузии на границах контактов между легированными областями стока и истока и кремния возникают локальные электрические поля, препятствующие дальнейшей диффузии и приводящие к образованию обед-ненного носителями слоя (Depletion Region). Поэтому в обычном состоянии прохождение тока между истоком и стоком невозможно. Для того чтобы иметь возможность переносить заряд между истоком и стоком, используется третий электрод, называемый затвором (Gate). Затвор отделен от кремниевой подложки слоем диэлектрика (Gate Oxide), в качестве которого выступает диоксид кремния (SiO2). При подаче потенциала на затвор создаваемое им электрическое поле вытесняет вглубь кремниевой подложки основные носители заряда кремния, а в образующуюся обедненную носителями область втягиваются основные носители заряда стока и истока. В результате между истоком и стоком в подзатворной области образуется своеобразный канал, насыщенный основными носителями заряда (Inversion Layer). Если теперь между истоком и стоком приложить напряжение, то по каналу пойдет ток. При этом принято говорить, что транзистор находится в открытом состоянии. При исчезновении потенциала на затворе канал разрушается и ток не проходит, то есть транзистор запирается.

Начиная со времени создания первой интегральной микросхемы все усилия электронной промышленности были направлены на то, чтобы уменьшить размеры транзистора. Так, в 1965 году в микросхемах интегрировалось всего три десятка транзисторов, а современный процессор насчитывает уже сотни миллионов транзисторов на кристалле.

В 1999 году, когда процессоры изготовлялись по 180-нм техпроцессу, длина затвора составляла 130 нм. Спустя десять лет, в 2009 году, был освоен 32-нм техпроцесс производства транзисторов с длиной затвора всего 15 нм (табл. 1).

Естественно, что уменьшение размеров транзистора сказывается не только на длине затвора, но и на других его характеристиках. Так, если считать, что длина затвора транзистора уменьшается в M раз, то в такое же число раз уменьшаются и толщина слоя диэлектрика, отделяющего область затвора от кремниевой подложки, и ширина затвора, и рабочее напряжение затвора. Кроме того, в M раз возрастает скорость работы транзистора и квадратично увеличивается плотность размещения транзисторов на кристалле, а рассеиваемая мощность уменьшается в M2 раз (табл. 2).

Конечно, в процессе эволюции планарных транзисторов менялись не только их размеры. Существенные изменения претерпели и используемые материалы, и даже геометрия самих транзисторов.

Дело в том, что основная проблема, связанная с уменьшением размеров транзистора, упирается даже не в технологические сложности литографического процесса, а в то, что экспоненциальное увеличение числа транзисторов на кристалле приводит к экспоненциальному росту потребляемой мощности и, как следствие, к перегреву микросхемы. Причина этого негативного явления заключается в том, что уменьшение размеров транзистора приводит к возникновению токов утечки. Токи утечки возникают через слой диэлектрика, отделяющего область затвора от кремниевой подложки, а также между истоком и стоком при «выключенном» состоянии транзистора.

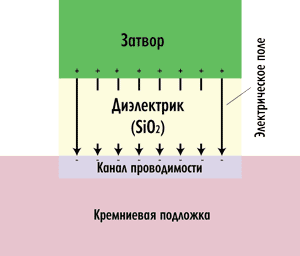

Рис. 2. Формирование емкости на затворе

Чтобы понять причину возникновения тока утечки, удобно рассматривать слой диэлектрика между затвором и кремнием как плоский конденсатор (рис. 2), емкость которого зависит от диэлектрической проницаемости вещества, толщины слоя диэлектрика и площади затвора по формуле:

C = (![]() 0kS)/d,

0kS)/d,

где S — площадь затвора, d — толщина слоя диэлектрика, k — диэлектрическая проницаемость слоя диэлектрика.

Понятие емкости затвора очень важно, так как в том числе и от нее зависит величина тока, проходящего между истоком и стоком. Действительно, поскольку емкость определяет способность накапливать заряд (Q=CU), то при одном и том же напряжении в случае большей емкости можно накопить больший заряд в канале проводимости, а следовательно, и создать больший ток. Таким образом, большая емкость позволяет снижать напряжение на затворе, что немаловажно при уменьшении размеров транзисторов. Кроме того, на ток в канале проводимости оказывает влияние и длина канала: чем она меньше, тем больший ток можно получить.

По мере сокращения размеров транзистора уменьшалась и толщина слоя диэлектрика. При этом между длиной канала и толщиной слоя диэлектрика соблюдается простое соотношение: толщина слоя диэлектрика приблизительно в 45 раз меньше длины канала.

В качестве диэлектрического слоя традиционно используется диоксид кремния (SiO2), диэлектрическая проницаемость которого составляет 3,9. Однако уменьшение толщины слоя диэлектрика, которое приводит к возрастанию емкости затвора, то есть положительно сказывается на характеристиках транзистора, имеет негативные последствия. Дело в том, что при достижении величины в несколько нанометров начинают сказываться эффекты туннелирования зарядов через слой диэлектрика, что приводит к возникновению токов утечки.

Данная проблема решается путем применения вместо диоксида кремния иных диэлектрических материалов, позволяющих использовать более толстые слои диэлектрика, но обеспечивающих, тем не менее, увеличение емкости затворного конденсатора. Такие материалы должны иметь более высокую диэлектрическую проницаемость и потому получили название High-K-диэлектрики. Понятно, что применение альтернативных материалов с более высокой диэлектрической проницаемостью позволяет во столько раз повысить толщину слоя ди-электрика по сравнению с толщиной диоксида кремния, во сколько раз диэлектрическая проницаемость вещества больше диэлектрической проницаемости диоксида кремния. Увеличение же слоя диэлектрика позволяет, в свою очередь, уменьшить токи утечки.

В качестве High-K-материалов могут использоваться различные соединения. Согласно информации компании Intel, большинство High-K-диэ-лектриков изготавливаются на основе гафния и циркония. К примеру, диоксид циркония (ZrO2) обладает диэлектрической проницаемостью равной 25, что в 6,4 раза больше, чем диэлектрическая проницаемость диоксида кремния. Следовательно, для обеспечения той же подзатворной емкости при применении диоксида циркония можно использовать в шесть с лишним раз более толстый слой диэлектрика, а это позволяет уменьшить ток утечки примерно в 10 тыс. раз.

Заменить диоксид кремния на High-K-ди-электрики с целью снижения токов утечки не так просто, как может показаться. И дело в данном случае не только в том, что придется менять технологический процесс производства микросхем, но и в том, что High-K-диэлектрики плохо сочетаются с поликристаллическим кремнием, из которого изготавливается затвор. В научной литературе есть данные, что использование структуры «High-K/поликремний» приводит к возникновению высокого порогового напряжения в планарных транзисторах, а кроме того, наблюдается значительное снижение активности движения электронов через канал из-за возникновения так называемого поверхностно-оптического фонового режима (SO) и связанного с ним снижения эксплуатационных характеристик транзистора вследствие поляризации High-K-слоя и инверсии заряда материала канала.

Поэтому второй важнейшей проблемой является поиск новых материалов для самого затвора, которые смогут заменить поликремний и будут хорошо сочетаться с High-K-ди-электриками. Такими материалами являются сплавы металлов, которые и используются в настоящее время при производстве транзисторов. Отметим, что транзисторы с металлическим затвором и High-K (затвор High-K/metal) применяются при производстве процессоров по 45-нм техпроцессу с 29 января 2007 года.

Конечно, мы рассказали только об одном из усовершенствований, которые претерпели планарные транзисторы. А таких усовершенствований за всю историю их развития было немало. Достаточно вспомнить такие технологии, как кремний на изоляторе (Silicon on Insulator, SOI), позволяющую снизить токи утечки между истоком и стоком, или технологию напряженного кремния, которая стала использоваться при изготовлении транзисторов NMOS и PMOS еще по 90-нм техпроцессу для улучшения их эксплуатационных характеристик. Технология создания напряжений позволяет увеличить подвижность как электронов, так и дырок и повышает скорость переключения транзисторов CMOS.

Одним словом, транзисторы постоянно совершенствуются, что позволяет электронной промышленности на протяжении последних 50 лет следовать закону Гордона Мура.

Последнее революционное усовершенствование структуры полевых транзисторов касается кардинального изменения их геометрии. Транзисторы перестали быть плоскими и обрели трехмерность.

Эра трехмерных транзисторов

Разработка трехмерной конструкции транзисторов началась еще в 2002 году. В сентябре 2002 года компания Intel объявила о разработке трехмерной конструкции транзистора с тройным затвором (Tri-gate), которая обеспечивает более эффективный расход энергии по сравнению с традиционными планарными транзисторами. Выступая с докладом, посвященным трехмерной конструкции транзистора с тройным затвором, доктор Джеральд Марчик (Gerald Marcyk), директор лаборатории изучения компонентов Intel, заявил: «Наши исследования показали, что по преодолении рубежа в 30 нм физическая основа плоских планарных транзисторов с одинарным затвором начинает давать утечку слишком большого количества энергии, что не позволит нам достичь желаемых целей в плане производительности. Конструкция транзистора с тройным затвором позволит Intel создавать сверхмалые транзисторы, которые обеспечат еще более высокую производительность при низком энергопотреблении и сделают возможным дальнейшее практическое воплощение закона Мура».

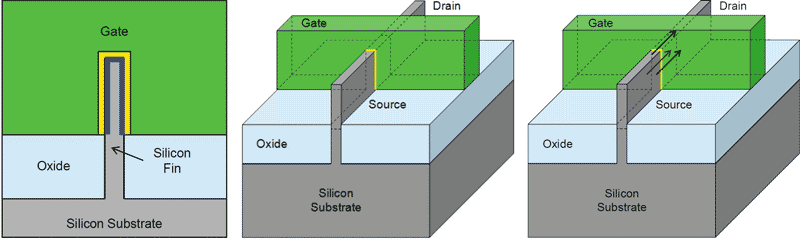

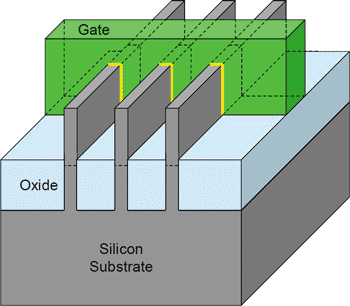

В основе трехмерного транзистора с тройным затвором лежит новаторская трехмерная структура, похожая на приподнятую горизонтальную плоскость с вертикальными стенками (рис. 3).

Рис. 3. Структура трехмерного транзистора с тройным затвором

Такая структура позволяет посылать электрические сигналы как по «крыше» транзистора, так и по обеим его «стенам». Фактически получается не один затвор, как в планарной структуре, а сразу три (две стенки и крышка). Отсюда и название «тройной затвор» (Tri-gate).

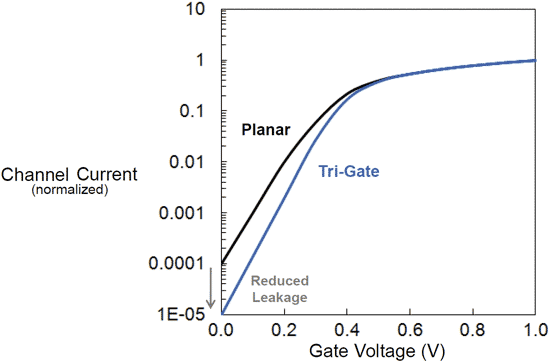

За счет подобной схемы распределения тока эффективно увеличивается площадь, доступная для прохождения тока; следовательно, снижается его плотность, а вместе с ней уменьшается и ток утечки (рис. 4). Тройной затвор строится на ультратонком слое полностью обедненного кремния, что обес-печивает еще большее снижение тока утечки и позволяет транзистору быстрее включаться и выключаться при значительном снижении энергопотребления.

Рис. 4. Снижение тока утечки в трехмерном трехзатворном транзисторе

Особенностью этой конструкции также являются поднятые исток и сток — в результате снижается сопротивление, что позволяет транзистору работать при токе меньшей мощности.

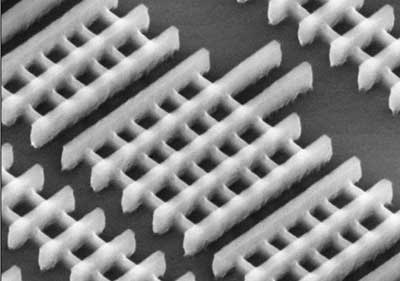

Использование трехмерной архитектуры транзистора с тройным затвором позволяет производить многоканальные трехзатворные транзисторы (Multi-Channel Tri-Gate Devices).

В таких устройствах применяется один трехмерный затвор, который сразу управляет прохождением тока между несколькими парами истоков и стоков, то есть одновременно образует множество каналов (рис. 5 и 6). Такая архитектура в еще большей степени позволяет повысить плотность размещения транзисторов на кристалле, а кроме того, повысить силу тока в транзисторе, поскольку суммарный ток, проходящий через транзистор, пропорционален количеству пар истоковстоков в транзисторе.

Рис. 5. Структура многоканального

трехзатворного транзистора

Рис. 6. Фотография многоканальных

трехзатворных транзисторов

Переход на новую структуру транзистора является революционным событием, так как до настоящего момента в массовой электронике использовались исключительно планарные структуры.

Трехмерные транзисторы с тройным затвором позволяют создавать процессоры, работающие при меньших значениях напряжения и с меньшими токами утечки, благодаря чему достигаются высокий уровень энергоэффективности и значительный прирост скорости работы по сравнению с существующими чипами.

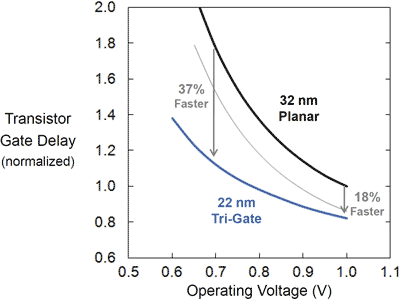

Трехмерные транзисторы Tri-Gate, изготовленные на базе 22-нм техпроцесса и работающие на низком напряжении, предлагают до 37% более высокую производительность по сравнению с обычными транзисторами, изготовленными на базе 32-нм технологии (рис. 7). Процессоры с новыми транзисторами могут потреблять менее половины мощности, чем 32-нм чипы с двумерной структурой, обеспечивая тот же уровень производительности.

Рис. 7. Увеличение производительности трехмерных транзисторов

Tri-Gate по сравнению

с планарными транзисторами

Переход на новые трехмерные транзисторы Tri-Gate будет осуществлен компанией Intel вместе с переходом на новую, 22-нм технологическую норму производства. Процессоры Intel Core под кодовым названием Ivy Bridge станут первыми массовыми чипами с транзисторами 3-D Tri-Gate. Серийное производство процессоров Ivy Bridge планируется начать в конце текущего года.