По следам IDF 2011: процессорная микроархитектура Intel Ivy Bridge

Кратко о процессорах Ivy Bridge

Особенности процессоров Sandy Bridge

Новый 22-нм техпроцесс: производство и трехмерные транзисторы

На прошедшем 13-15 сентября форуме IDF 2011 компания Intel впервые сообщила информацию о новой процессорной микроархитектуре, известной под кодовым наименованием Ivy Bridge. Однако достоянием гласности стали далеко не все подробности. Некоторые сведения останутся в тайне до официального анонса, который должен состояться в конце года. В частности, не были разглашены данные, касающиеся производительности новых процессоров, модельного ряда, частот, размеров кэша, а также некоторых других характеристик.

Итак, давайте поближе познакомимся с новой микроархитектурой Ivy Bridge, а также с особенностями процессоров на ее основе, которые в дальнейшем мы будем называть Ivy Bridge.

Кратко о процессорах Ivy Bridge

В течение уже многих лет выход новых поколений процессоров Intel подчиняется эмпирическому правилу TICK-TOCK («тиктак»), суть которого заключается в том, что перевод производства на новый технологический процесс (TICK) и внедрение новой процессорной микроархитектуры (TOCK) происходят поочередно с периодичностью примерно в два года. Например, если в первый год происходит переход на новый техпроцесс производства, то на второй год на этом же техпроцессе внедряется новая процессорная микроархитектура. На следующий год происходит перенос микроархитектуры на новый техпроцесс производства. Так, первые процессоры, выпускаемые по 32-нм техпроцессу, имели кодовое название Westmere и были основаны на микроархитектуре Nehalem (цикл TICK). Затем, в конце прошлого года, компания Intel выпустила 32-нм процессоры Sandy Bridge на базе новой микроархитектуры (цикл TOCK). Соответственно в конце этого года компания должна выпустить уже 22-нм версию процессоров на базе микроархитектуры Sandy Bridge, которые получат кодовое наименование Ivy Bridge (цикл TICK).

Тем не менее процессоры Ivy Bridge — это не просто 22-нм версия процессоров Sandy Bridge. В данном случае речь идет и о существенной модернизации самой микроархитектуры. Именно поэтому компания Intel называет этот переход на новый техпроцесс не просто циклом TICK, а циклом TICK+.

Итак, давайте рассмотрим, чем процессоры Ivy Bridge отличаются от Sandy Bridge и почему новые процессоры — это не просто 22-нм версия процессоров предыдущего поколения. Однако прежде вкратце напомним основные особенности процессоров Sandy Bridge.

Особенности процессоров Sandy Bridge

Процессоры Sandy Bridge имеют разъем LGA 1155 и совместимы с чипсетами Intel 6-й серии. Процессоры Ivy Bridge также будут иметь разъем LGA 1155 и будут совместимы и с чипсетами Intel 6-й серии, и с новыми чипсетами Intel 7-й серии. То есть новые процессоры могут быть совместимы (но необязательно) с материнскими платами на чипсетах Intel 6-й серии, а процессоры Sandy Bridge, скорее всего, будут совместимы с материнскими платами на чипсетах Intel 7-й серии.

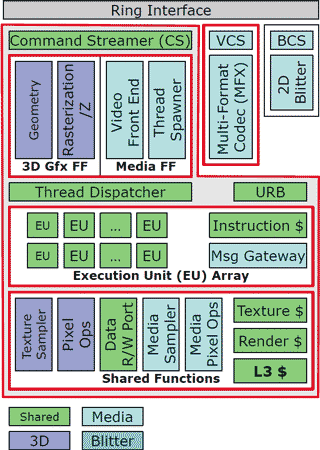

Отличительной особенностью процессоров Sandy Bridge является наличие в них интегрированного графического ядра, которое не просто размещается на одном кристалле с вычислительными ядрами процессора, но и производится по 32-нм техпроцессу. Причем идеологически графическое ядро процессора Sandy Bridge можно рассматривать как еще одно ядро процессора, которое, так же как и вычислительные ядра процессора, имеет доступ к кэшу L3.

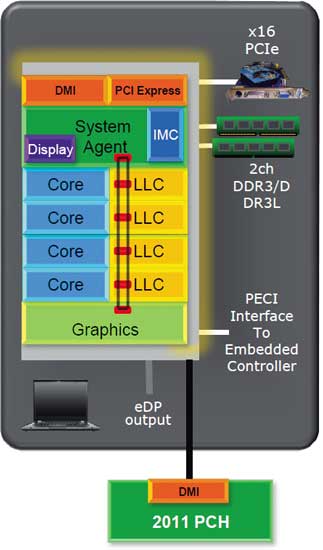

Блок-схема процессора Ivy Bridge

Однако в процессоре Ivy Bridge будет использоваться совершенно новое графическое ядро (с новой микроархитектурой) с поддержкой DirectX 11, о чем далее мы расскажем более подробно.

Процессор Ivy Bridge, так же как и процессор Sandy Bridge, будет иметь интегрированный контроллер PCI Express на 16 линий для использования дискретных видеокарт. Однако если в случае процессора Sandy Bridge речь шла о контроллере PCI Express 2.0, то в процессорах Ivy Bridge будет применяться контроллер PCI Express 3.0.

Разница в пропускной способности интерфейсов PCI Express 2.0 и 3.0 весьма существенная. Так, для интерфейса PCI Express 2.0 пропускная способность каждой линии составляет 500 Мбайт/с в каждом направлении, а для интерфейса PCI Express 3.0 — 1 Гбайт/с в каждом направлении. Нетрудно подсчитать, что для интерфейса PCI Express 3.0 x16 пропускная способность составит уже 32 Гбайт/с.

Конечно, для реализации возможностей интерфейса PCI Express 3.0 в процессоре Ivy Bridge нужна еще видеокарта с аналогичным интерфейсом. Пока таких видеокарт на рынке нет, но, по всей видимости, в скором времени они появятся.

В процессоре Ivy Bridge, как и в процессоре Sandy Bridge, будет встроен двухканальный контроллер памяти DDR3. Однако контроллер памяти в процессоре Ivy Bridge будет поддерживать более скоростную и низковольтную память.

Новый 22-нм техпроцесс: производство и трехмерные транзисторы

Итак, самое главное отличие процессоров Ivy Bridge от Sandy Bridge заключается в том, что они изготавливаются по 22-нм техпроцессу (процессоры Sandy Bridge производятся по 32-нм техпроцессу).

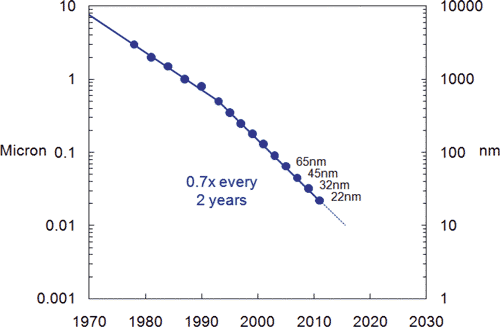

Вообще, переход на новый техпроцесс производства подчиняется эмпирическому правилу 0,7x, то есть каждый новый техпроцесс масштабируется в 0,7 раза. Естественно, что уменьшение геометрических размеров транзистора сказывается на всех характеристиках транзистора.

Масштабирование техпроцесса производства процессоров Intel

Так, если считать, что геометрические размеры транзистора (длина и ширина затвора, толщина слоя диэлектрика, ширина затвора) уменьшаются в K раз, то в такое же количество раз уменьшатся рабочее напряжение затвора, ток и емкость подзатворной области. Кроме того, в K раз возрастет скорость работы транзистора, квадратично увеличится плотность размещения транзисторов на кристалле, а рассеиваемая мощность квадратично уменьшится.

Основная проблема, связанная с уменьшением размеров транзистора, заключается в том, что экспоненциальное увеличение числа транзисторов на кристалле приводит к экспоненциальному росту потребляемой мощности и, как следствие, к перегреву микросхемы. Причина этого негативного явления заключается в том, что уменьшение размеров транзистора приводит к возникновению токов утечки. Токи утечки возникают через слой диэлектрика, отделяющего область затвора от кремниевой подложки, а также между истоком и стоком при «выключенном» состоянии транзистора.

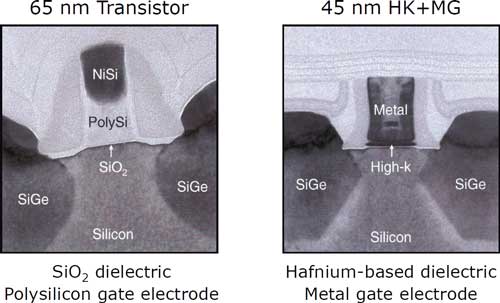

Транзисторы с подзатворным диэлектриком SiO2 и затвором High-K/metal

Чтобы понять причину возникновения тока утечки, удобно рассматривать слой диэлектрика между затвором и кремнием как плоский конденсатор. Понятие емкости затвора очень важно, так как в том числе и от нее зависит величина тока, проходящего между истоком и стоком. Действительно, поскольку емкость определяет способность накапливать заряд, то при одном и том же напряжении в случае большей емкости можно накопить больший заряд в канале проводимости, а следовательно, создать больший ток. Таким образом, большая емкость позволяет снижать напряжение на затворе, что немаловажно при уменьшении размеров транзисторов.

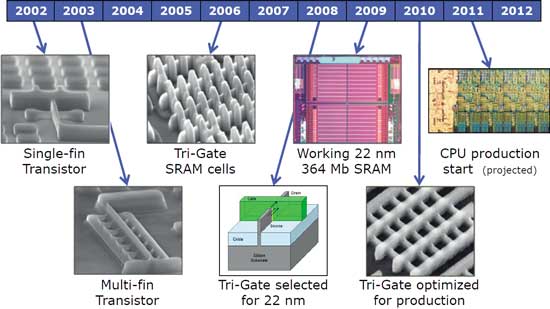

История создания Tri-Gate-транзистора

Как уже отмечалось, при сокращении размеров транзистора уменьшается и толщина слоя диэлектрика. Однако уменьшение толщины слоя диэлектрика, которое приводит к возрастанию емкости затвора, то есть положительно сказывается на характеристиках транзистора, имеет свои негативные последствия. Дело в том, что при достижении величины в несколько нанометров начинают возникать эффекты туннелирования зарядов через слой диэлектрика, что приводит к возникновению токов утечки.

Данная проблема частично решается путем применения вместо диоксида кремния, который на протяжении многих лет использовался в качестве диэлектрика в транзисторах, иных диэлектрических материалов, позволяющих применять более толстые слои диэлектрика, но обеспечивающих, тем не менее, увеличение емкости подзатворного конденсатора. Такие материалы должны иметь более высокую диэлектрическую проницаемость, а потому получили название High-K-диэлектрики. Понятно, что применение альтернативных материалов с более высокой диэлектрической проницаемостью позволяет во столько раз повысить толщину слоя диэлектрика по сравнению с толщиной диоксида кремния, во сколько раз диэлектрическая проницаемость вещества больше диэлектрической проницаемости диоксида кремния. Увеличение же слоя диэлектрика, в свою очередь, позволяет уменьшить токи утечки.

Именно поэтому диоксид кремния больше не используется в качестве диэлектрика в транзисторах. Начиная с 45-нм техпроцесса производства при изготовлении процессоров применяются транзисторы с High-K-диэлектриками (затвор High-K/metal).

Конечно, использование High-K-диэлектриков — это лишь одно из усовершенствований, которые претерпели планарные транзисторы. Можно также вспомнить технологию напряженного кремния, которая стала применяться при изготовлении транзисторов NMOS и PMOS еще по 90-нм техпроцессу для улучшения их эксплуатационных характеристик. Технология создания напряжений позволяет увеличить подвижность как электронов, так и дырок и повышает скорость переключения транзисторов.

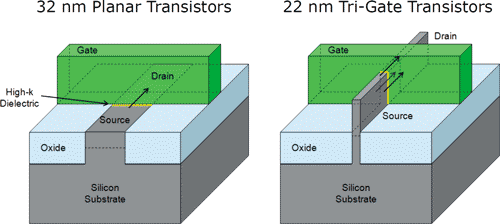

Планарный и Tri-Gate-транзисторы

Последнее революционное усовершенствование структуры полевых транзисторов касается кардинального изменения их геометрии — транзисторы из плоских превратились в трехмерные. Разработка трехмерной конструкции транзисторов началась еще в 2002 году. В сентябре 2002-го компания Intel объявила о разработке трехмерной конструкции транзистора с тройным затвором (Tri-gate), которая обеспечивает более эффективный расход энергии по сравнению с традиционными планарными транзисторами.

В основе трехмерного транзистора с тройным затвором лежит трехмерная структура, похожая на приподнятую горизонтальную плоскость с вертикальными стенками.

Такая структура позволяет посылать электрические сигналы как по «крыше» транзистора, так и по обеим его «стенам». Фактически получается как бы не один затвор, как в планарой структуре, а сразу три (две стенки и крышка). Отсюда и название — «тройной затвор» (Tri-gate).

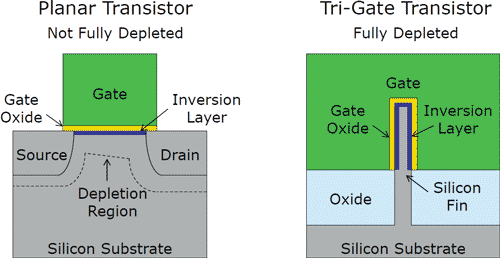

Сравнение Tri-Gate и планарного транзисторов

Благодаря подобной схеме распределения тока эффективно увеличивается площадь, доступная для прохождения тока, а следовательно, снижается его плотность, а вместе с ней уменьшается ток утечки. Тройной затвор строится на ультратонком слое полностью обедненного кремния, что обеспечивает еще большее снижение тока утечки и позволяет транзистору быстрее включаться и выключаться при значительном снижении энергопотребления.

Особенностью этой конструкции также являются поднятые исток и сток — в результате уменьшается сопротивление, что позволяет транзистору работать при токе меньшей мощности.

Несмотря на тот факт, что разработка трехмерной конструкции транзисторов началась еще в 2002 году, их использование в производстве процессоров стало возможно лишь спустя почти 10 лет, то есть при переходе на 22-нм техпроцесс производства.

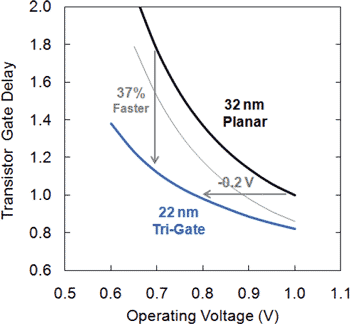

Трехмерные транзисторы Tri-Gate, изготовленные на базе 22-нм техпроцесса и работающие на низком напряжении, обеспечивают до 37% более высокую производительность в сравнении с обычными транзисторами, изготовленными на базе 32-нм технологии. Процессоры с новыми транзисторами могут потреблять менее половины мощности по сравнению с 32-нм чипами с двумерной структурой, сохраняя тот же уровень производительности.

Сопоставление характеристик планарного

и Tri-Gate-транзисторов

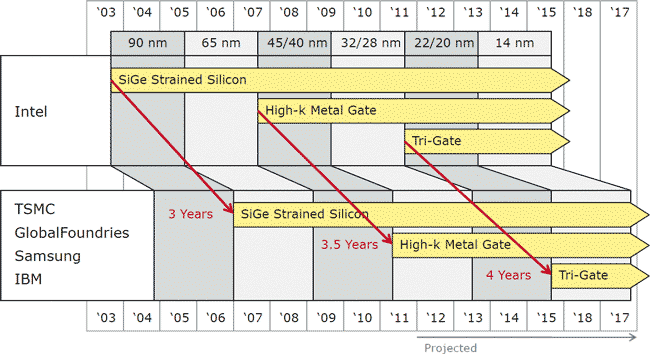

Отметим также, что компания Intel стала первой применять трехмерные транзисторы при производстве микросхем. Все остальные компании, занимающиеся производством микросхем, смогут наладить производство трехмерных транзисторов не ранее чем через четыре года.

Итак, одно из главных нововведений в 22-нм процессорах Ivy Bridge — использование более производительных и энергоэффективных трехмерных Tri-Gate-транзисторов. Однако это не единственное отличие 22-нм процессоров Ivy Bridge от 32-нм процессоров Sandy Bridge.

Вычислительное ядро

Что касается вычислительного ядра процессора Ivy Bridge, то оно не претерпело изменений в сравнении с вычислительным ядром Sandy Bridge (во всяком случае, о какихлибо изменениях пока не упоминалось). А потому лишь вкратце коснемся архитектуры ядра Sandy Bridge/Ivy Bridge.

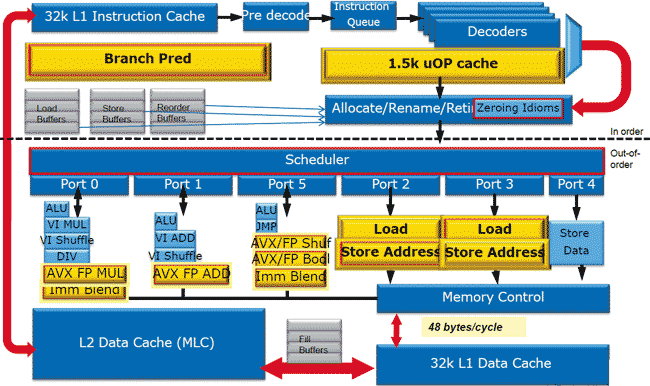

Итак, при работе вычислительного ядра процессора на базе микроархитектуры Ivy Bridge инструкции x86 выбираются из кэша инструкций L1 (Instruction Сache) размером 32 Кбайт (кэш 8-канальный). Команды загружают 16-байтными блоками, то есть за каждый такт из кэша загружается 16-байтный блок команд. Поскольку инструкции x86 имеют переменную длину, а длина блоков, которыми команды загружаются из кэша, фиксированная, при декодировании команд нужно определить границы между отдельными командами. Информация о размерах команд хранится в кэше инструкций L1 в специальных полях, а сама процедура выделения команд из выбранного блока называется предварительным декодированием (PreDecode).

Лидерство компании Intel в освоении новых технологий производства микросхем

После операции выборки команды организуются в очередь (Instruction Queue), а затем передаются в декодер. При декодировании (Decode) команды преобразуются в машинные микрооперации (обозначаются как micro-ops или uOps).

Декодер ядра процессора с микроархитектурой Ivy Bridge является четырехканальным и может декодировать в каждом такте до четырех инструкций x86. В принципе, длина одной команды может достигать 16 байт, однако средняя длина команд составляет 4 байта. Поэтому в среднем в каждом 16-байтном блоке загружается четыре команды, которые при использовании четырехканального декодера одновременно декодируются за один такт.

Четырехканальный декодер состоит из трех простых декодеров, декодирующих простые инструкции в одну микрооперацию, и одного сложного, который способен декодировать одну инструкцию в четыре микрооперации (декодер типа 4-1-1-1). Для еще более сложных инструкций, декодирующихся более чем в четыре микрооперации, сложный декодер соединен с блоком uCode Sequenser, который и применяется для декодирования подобных инструкций.

При декодировании инструкций используются технологии Macro-Fusion и Micro-Fusion.

Macro-Fusion — это слияние двух x86-инструкций в одну сложную микрооперацию micro-ops, которая в дальнейшем будет выполняться именно как одна микрооперация. Естественно, такому слиянию могут подвергаться не любые инструкции, а только некоторые пары инструкций (например, инструкция сравнения и условного перехода).

Micro-Fusion — это слияние двух микроопераций в одну, содержащую два элементарных действия. В дальнейшем две такие слитые микрооперации обрабатываются как одна, что в результате позволяет снизить количество обрабатываемых микроопераций и тем самым увеличить общее количество исполняемых процессором инструкций за один такт. Понятно, что операция слияния двух микроопераций возможна далеко не для всех пар микроопераций.

Говоря о процедуре выборки программных инструкций, необходимо отметить наличие блока обнаружения программных циклов Loop Stream Detector (LSD), который принимает непосредственное участие в процессе выборки инструкций и позволяет избежать повторов в выполнении одних и тех же операций. В ядрах на базе микроархитектуры Ivy Bridge/Sandy Bridge LSD блок расположен за декодером и рассчитан на 28 уже декодированных инструкций. Поскольку LSD хранит уже декодированные инструкции, при обнаружении циклов будет пропускаться фаза предсказания ветвлений, выборки и декодирования (фактически на время выполнения программного цикла отключается предпроцессор процессора). Таким образом, инструкции в цикле проходят через конвейер быстрее и чаще, а энергопотребление снижается.

Кроме того, применяется кэш декодированных микроопераций (Decoded Uop Cache), в который поступают все декодированные микрооперации. Он рассчитан приблизительно на 1500 микроопераций средней длины. Концепция кэша декодированных микроопераций заключается в том, чтобы сохранять в нем уже декодированные последовательности микроопераций. В результате, если нужно выполнить некую x86-инструкцию повторно и соответствующая ей последовательность декодированных микроопераций всё еще находится в кэше декодированных микроопераций, то нет необходимости вторично выбирать эту инструкцию из кэша L1 и декодировать ее — уже декодированные микрооперации поступают из кэша на дальнейшую обработку.

После процесса декодирования x86-инструкций начинается этап их исполнения. Первоначально происходит переименование и распределение дополнительных регистров процессора (блок Allocate/Rename/Retirement), которые не определены архитектурой набора команд. Переименование регистров позволяет добиться исполнения команд вне очереди, а следовательно, снизить простои процессора.

На следующем этапе происходит переупорядочение микроопераций не в порядке их поступления (Out-of-Order), чтобы впоследствии можно было реализовать их более эффективное выполнение на исполнительных блоках.

Далее происходит распределение микроопераций по исполнительным блокам. В блоке процессора Reservation Station формирует очереди микроопераций, в результате чего микрооперации попадают на один из портов функциональных устройств (dispatch ports). Этот процесс называется диспетчеризацией (Dispatch), а сами порты выполняют функцию шлюза к функциональным устройствам.

Блок-схема вычислительного ядра Sandy Bridge/Ivy Bridge

В микроархитектуре Sandy Bridge кластер Allocate/Rename/Retirement (Out-of-Order Cluster) был существенно изменен в сравнении с микроархитектурой предыдущего поколения Nehalem. Так, в микроархитектуре Nehalem каждая микрооперация имеет копию операнда или нескольких операндов, которые ей требуются. Фактически это означает, что блоки кластера внеочередного выполнения команд должны быть достаточно большого размера, чтобы вмещать микрооперации вместе с требуемыми им операндами.

Вместо этого в микроархитектуре Sandy Bridge (соответственно и в микроархитетуре Ivy Bridge) используется физический регистровый файл (Physical Register File, PRF), в котором хранятся операнды микроопераций. Это позволяет микрооперациям сохранять лишь указатели на операнды, но не сами операнды. С одной стороны, такой подход обеспечивает снижение энергопотребления процессора, поскольку перемещение по конвейеру микроопераций вместе с их операндами требует существенных затрат по энергопотреблению. С другой стороны, применение физического регистрового файла позволяет сэкономить на размере кристалла, а высвободившееся пространство использовать для увеличения размеров буферов кластера внеочередного выполнения команд. В ядрах Sandy Bridge/Ivy Bridge физический регистровый файл для целочисленных операндов (PRF Integer) рассчитан на 160 записей, а для операндов с плавающей запятой (PRF Float Point) — на 144 записи.

Если говорить об исполнительных блоках ядра процессора Ivy Bridge, то портов функциональных устройств насчитывается шесть (три вычислительных и три для работы с памятью). При этом три вычислительных устройства позволяют проводить восемь операций с данными FP (Float Point) или две операции с 256-битными AVX-данными за такт.

Из трех портов для работы с памятью два являются универсальными и могут реализовывать загрузку данных (Load) или сохранять адрес (Store address). Третий порт предназначен для хранения данных (Store data). Соответственно пропускная способность взаимодействия с кэшем данных L1 составляет 48 байт за такт (два запроса на чтение по 16 байт и один запрос на запись до 16 байт данных).

Кольцевая шина

Напомним, что в микроархитектуре Sandy Bridge впервые стала применяться кольцевая шина (Ring Bus), по которой происходит обмен данными между кэшами L2 каждого ядра процессора и кэшем L3, реализуется доступ графического ядра (GPU) и блока видеокодирования (video transcoding engine) к кэшу L3. Кроме того, по этой же кольцевой шине обеспечивается доступ к контроллеру памяти.

Кольцевая шина объединяет четыре отдельные шины: кольцевую шину данных (Data ring) разрядностью 256 бит (32 байт), кольцевую шину запросов (Request ring), шину подтверждений (Acknowledge ring) и следящую шину (Snoop ring).

Весь L3-кэш разбит на отдельные участки, каждый из которых ассоциирован с отдельным ядром процессора. В то же время каждому ядру доступен весь кэш L3. Каждый из выделенных участков кэша L3 наделен агентом доступа к кольцевой шине. Аналогичные агенты доступа имеются у кэшей L2 каждого ядра процессора, у графического ядра и у системного агента, реализующего обмен данными с контроллером памяти.

Остается лишь добавить, что в микроархитектуре Ive Bridge используется точно такая же кольцевая шина, как в микроархитектуре Sandy Bridge.

Графическое ядро

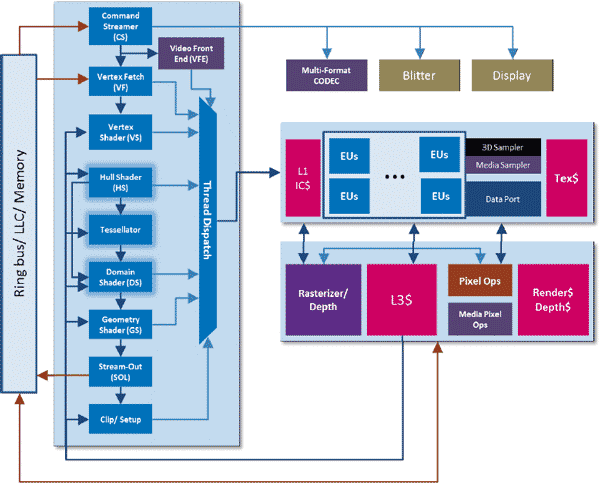

Одно из главных нововведений в микроархитектуре Ivy Bridge — это новое графическое ядро с поддержкой DirectX 11, которое имеет кодовое название Carlow.

Конечно, графическое ядро в процессорах Ivy Bridge по производительности не может сравниться с дискретной графикой, но справедливости ради отметим, что оно и не позиционируется как игровое.

В то же время, по заявлению компании Intel, графическое ядро в процессорах Ivy Bridge будет на 60% более производительным, чем графическое ядро в процессорах Sandy Bridge. Собственно, если это действительно так, то новая графика от Intel сможет вполне успешно конкурировать с процессорной графикой AMD.

Кроме поддержки DirectX 11, в графическом ядре Carlow будет реализована поддержка OpenGL 3.1 и OpenCL 1.1, то есть графическое ядро Intel будет способно производить вычисления средствами шейдерных процессоров.

3D-блок ядра Carlow

Напомним, что в процессоре Sandy Bridge графическое ядро содержит (в зависимости от модели процессора) шесть или 12 исполнительных блоков (Execution Unit, EU), в каждом из которых по одному текстурному блоку. В графическом ядре Ivy Bridge максимальное число исполнительных блоков увеличено до 16, причем на каждый исполнительный блок приходится уже по два текстурных блока.

В графическое ядро Ivy Bridge добавлены блоки для аппаратной тесселяции, а также обеспечена поддержка Shader Array (что, собственно, и позволило добиться совместимости с Shader Model 5.0 и DirectX 11).

Интересно отметить, что тактовая частота графического ядра процессора Ivy Bridge ниже, чем частота графического ядра процессора Sandy Bridge, что позволяет уменьшить энергопотребление. В результате по такому показателю, как производительность на ватт, графическое ядро Carlow вдвое превосходит ядро HD Graphics 2000/3000 в процессоре Sandy Bridge.

Блок-схема графического ядра Carlow

Изменения коснулись и технологии Intel Quick Sync. Прежде всего, производитель обещает двукратное увеличение скорости перекодирования HD-видео с применением специализированных процессорных блоков. Кроме того, заявлено улучшение качества кодирования и добавление возможности применения к перекодируемому видеопотоку фильтров типа улучшения цветовой гаммы или контрастности.

Мощности аппаратного видеодекодера будет достаточно для одновременного воспроизведения не менее 16 HD-видеопотоков.

Конфигурируемый TDP

Еще одно нововведение в процессорах Ivy Bridge — это конфигурируемый TDP. Напомним, что TDP является одной из важнейших характеристик процессоров Intel. В частности, значение TDP определяет и максимальное энергопотребление процессора, и необходимую эффективность системы охлаждения. К значению TDP привязывается возможность повышения тактовой частоты ядер процессора в режиме Turbo Boost (то есть тактовая частота может повышаться, только если не превышено значение TDP или это превышение кратковременное).

В процессорах Ivy Bridge будет определено не одно, а три значения TDP: минимальное, номинальное и турбо. То есть при достаточном теплоотводе TDP процессора может быть повышено и соответственно увеличится его тактовая частота в режиме Turbo Boost. Если же нужно максимально уменьшить энергопотребление, то TDP можно снизить. Причем предполагается, что устанавливать одно из трех значений TDP будет сам пользователь (видимо, с помощью соответствующего софта).

Понятно, что технология конфигурируемого TDP направлена прежде всего на мобильные процессоры. Так, если ноутбук питается от сети и обеспечивается достаточное охлаждение процессора, то TDP можно увеличить. Если же ноутбук работает в автономном режиме, то с целью увеличения времени автономной работы TDP процессора желательно снизить.

Важно отметить, что технология конфигурируемого TDP не заменяет собой технологию Intel Speed Step или выбор схемы энергопотребления процессора в настройках операционной системы. Она лишь дополняет уже имеющиеся технологии.

Разгон процессоров

Напомним, что в процессорах Sandy Bridge с разблокированным коэффициентом умножения (процессоры К-серии) максимальный коэффициент умножения был равен 57. То есть даже теоретически процессоры Sandy Bridge нельзя было разогнать выше частоты 5,7 ГГц (процессоры Sandy Bridge практически невозможно разогнать за счет повышения частоты системной шины). В процессорах Ivy Bridge максимальный коэффициент умножения повышен до значения 63, то есть путем изменения коэффициента умножения процессор теоретически можно будет разогнать до частоты 6,3 ГГц.

Еще одно нововведение — это поддержка процессорами Ivy Bridge более скоростной памяти. Напомним, что у процессоров Sandy Bridge максимальная частота памяти DDR3 может составлять только 2133 МГц. Таким образом, процессоры Ivy Bridge будут поддерживать память с частотой выше 2133 МГц (естественно, речь идет о разгонном режиме работы процессора).

Еще одно новшество в плане разгонных возможностей процессора Ivy Bridge — это изменение коэффициента умножения без необходимости перезагрузки системы.

Прочие нововведения

Очередное нововведение в процессоре Ivy Bridge — это наличие аппаратного генератора случайных чисел (Digital Random Number Generator, DRNG), который находит применение в криптографических задачах. Вообще, генераторы случайных чисел уже давно используются в процессорах. Однако до сих пор речь шла о псевдослучайных генераторах, которые работают в соответствии с определенным математическим алгоритмом. В процессоре Ivy Bridge речь идет о реальном (не псевдослучайном) генераторе случайных чисел, в основе которого лежит электронная схема с неопределенным состоянием, что позволяет генерировать поток случайных символов в 16-, 32- или 64-битном формате со скоростью 2 или 3 Гбит/с.

К нововведениям также можно отнести режим Supervisory Mode Execute Protection (SMEP), представляющий собой реализацию технологии защиты от повышения уровня привилегий. Данная технология контролирует уровень привилегий исполняемого кода, который размещен в адресном пространстве, выделенном для работы программам (Applications). Благодаря этому на аппаратном уровне блокируется классическая атака, нацеленная на повышение уровня привилегий и необходимая для получения доступа к системным ресурсам.

Чипсеты Intel 7-й серии

Некоторые китайские производители, пытаясь бежать быстрее паровоза, уже сейчас заявляют о том, что их материнские платы на базе чипсетов Intel 6-й серии поддерживают PCI Express v.3.0. На самом деле поддержка PCI Express v.3.0 на платах с чипсетами Intel 6-й серии сегодня никому не нужна. А когда появятся процессоры Ivy Bridge с поддержкой PCI Express v.3.0, а также видеокарты с поддержкой этого скоростного интерфейса, то платы с чипсетами Intel 6-й серии уже морально устареют. А устанавливать новые процессоры Ivy Bridge в старые материнские платы с чипсетами Intel 6-й серии, несмотря на их совместимость, абсолютно нелогично, тем более что одновременно с новыми процессорами Ivy Bridge будут анонсированы и новые чипсеты Intel 7-й серии.

Отличительной особенностью чипсетов Intel 7-й серии будет поддержка портов USB 3.0 и SATA 6 Гбит/с.

Сейчас у нас есть информация о трех чипсетах Intel 7-й серии для десктопных процессоров: Intel Z77, Z75 и H77 (см. таблицу). Собственно, все три чипсета поддерживают процессорное графическое ядро, имеют по восемь дополнительных линий PCI Express 2.0, поддерживают по десять портов USB 2.0 и по четыре порта USB 3.0, по четыре порта SATA 3 Гбит/с и по два порта SATA 6 Гбит/с. Кроме того, у всех чипсетов реализована возможность создания RAID-массивов. Разница между чипсетами заключается лишь в возможности разгона процессора, поддержке технологии Intel Smart Response и поддерживаемых конфигурациях слотов PCI Express, которые реализуются через 16 линий PCI Express 3.0, поддерживаемых процессором Ivy Bridge.

Как видите, самым функциональным является чипсет Intel Z77, который поддерживает технологию Intel Smart Response и позволяет разгонять процессор. Кроме того, он дает возможность реализовать три варианта конфигурации слотов PCI Express через 16 линий PCI Express 3.0, поддерживаемых процессором Ivy Bridge. Это может быть только один слот PCI Express 3.0, функционирующий в режиме x16, либо два слота PCI Express 3.0 х8, либо один слот PCI Express 3.0 х8 и два слота PCI Express 3.0 х4.

Чипсет Intel Z75 имеет несколько более скромные возможности. Он также позволяет разгонять процессор, однако не поддерживает технологию Intel Smart Response. Кроме того, этот чипсет дает возможность реализовать только два варианта конфигурации слотов PCI Express — это может быть только один слот PCI Express 3.0, функционирующий в режиме x16, либо два слота PCI Express 3.0 х8.

Чипсет Intel H77 является младшей моделью в данной линейке и ориентирован на бюджетные материнские платы. Он поддерживает технологию Intel Smart Response, однако не дает возможность разгонять процессор. Кроме того, он позволяет сгруппировать 16 линий PCI Express 3.0, поддерживаемых процессором Ivy Bridge, только в порт PCI Express 3.0 х16.