Встречаем процессор AMD Trinity для настольных ПК

Графическое ядро в APU Trinity

В мае компания AMD представила мобильные процессоры семейства Trinity, а октябрь ознаменовался выходом процессоров AMD Trinity для настольных ПК. В этой статье мы подробно рассмотрим результаты тестирования нового топового десктопного процессора AMD A10-5800К семейства Trinity и сравним его с процессором Intel Core i7-3770K.

Общие сведения

Процессоры семейства AMD Trinity представляют собой очередной виток в развитии рынка гибридных процессоров AMD, называемых APU (Accelerated Processing Unit).

Напомним, что APU — это реализация процессоров AMD с интегрированным графическим ядром. Первые гибридные процессоры APU были представлены в 2011 году, когда компания AMD выпустила процессоры Brazos серий E и C, ориентированные на рынок бюджетных ноутбуков. Позднее были анонсированы гибридные процессоры с кодовым наименованием Llano, предназначенные для рынка настольных ПК и производительных ноутбуков.

Гибридные процессоры AMD Trinity ориентированы на тот же сегмент рынка, что и процессоры Llano, а потому можно сказать, что APU Trinity пришли на смену APU Llano.

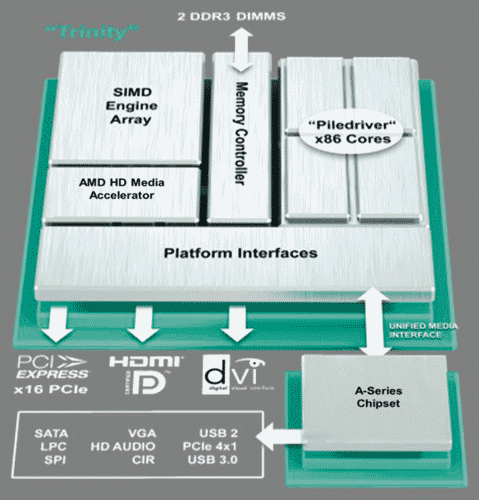

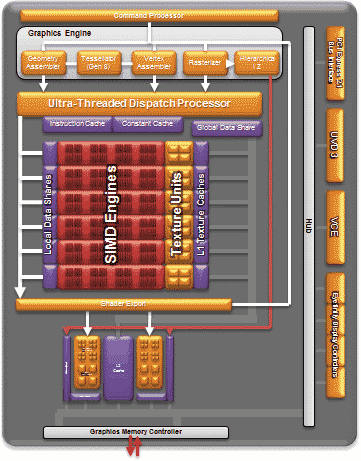

Конструктивно процессоры AMD Trinity, так же как и процессоры Llano, имеют два или четыре вычислительных ядра x86 и графическое ядро (рис. 1). Однако и сами вычислительные ядра процессора Trinity, и его графическое ядро существенно отличаются от того, что имеется в Llano.

Рис. 1. Структурная схема процессора AMD Trinity

Если процессоры Llano включали вычислительные ядра с микроархитектурой Phenom II (кодовое наименование Stars), то основу процессоров Trinity составляют вычислительные ядра c микроархитектурой Piledriver, которая является улучшенным вариантом микроархитектуры Bulldozer.

Графическое ядро процессоров семейства Trinity имеет кодовое наименование Northern Islands и содержит 384 вычислительных ядра. Графическое ядро Trinity основано на суперскалярной архитектуре VLIW4 (в процессорах Llano графическое ядро имело архитектуру VLIW5).

Кроме того, если процессоры семейства Llano для настольных ПК имеют разъем Socket FM1, то новые процессоры Trinity оснащены разъемом Socket FM2 (904 контакта). Хотя внешне разъемы практически одинаковые, новые процессоры по разъему несовместимы со старыми, соответственно и старые процессоры в новый разъем установить нельзя.

APU Trinity, так же как и Llanо, производится по 32-нм техпроцессу SOI на мощностях Global Foundries c использованием транзисторов с high-k-диэлектриками и металлическим затвором. Он содержит 1,3 млрд транзисторов, что немного больше, чем в APU Llano. Площадь кристалла APU Trinity тоже побольше и составляет 246 мм2 (площадь кристалла процессора Llano — 228 мм2).

Все APU Trinity имеют интегрированный контроллер PCI Express 2.0 на 20 линий, причем 16 линий PCI Express 2.0 — это линии общего назначения (PEG/GPP), которые служат для организации слотов для дискретных графических карт или других карт расширения, а еще четыре линии PCI Express 2.0 (только GPP) имеют ограничение — они не могут применяться для создания слота для дискретной видеокарты и могут использоваться только для интегрированных контроллеров и создания слотов для карт расширения. Кроме того, в процессор Trinity интегрированы двухканальный контроллер памяти с поддержкой модулей до DDR3-1866 и кэш L2 размером из расчета по 1 Мбайт на каждое ядро (L3-кэш отсутствует).

Кроме того, все процессоры Trinity поддерживают технологию динамического разгона новой версии Turbo Core 3.0, которая немного отличается от той, что использовалась ранее. Различие между ними состоит в том, что в Turbo Core 3.0 компания AMD реализовала автоматическое повышение частоты каждого из ядер на различные значения. То есть каждое ядро, в зависимости от нагрузки, может повышать свою частоту независимо от других ядер, если при этом общее энергопотребление не выходит за рамки TDP. Кроме того, теперь эта технология динамически меняет частоту не только вычислительных ядер, но и графического ядра.

Еще одно различие между Llano и Trinity заключается в том, что в Llano использовалась шина HyperTransport и Fusion Control Link для взаимодействия графического ядра с памятью. В новых процессорах Trinity эти шины заменяет объединенный северный мост под названием Unified NorthBridge. В данном случае это первая реализация Unified NorthBridge от AMD в процессорах для настольных ПК, а не для серверов. Данный компонент связывает остальные модули с памятью и подсистемой вводавывода. Он предназначен для обслуживания различных функциональных блоков, каждый из которых делает особые запросы со специфическими параметрами. Так, модули центрального процессора отправляют незначительное количество запросов по шине UNB, но при этом они имеют высокий приоритет, поскольку дополнительная задержка может серьезно повлиять на производительность. При этом графическое ядро активно использует память для обработки поступающей информации, но скорость обработки в этом случае не так важна. Шина UNB построена таким образом, чтобы оптимизировать и направлять запросы для оптимального применения всеми модулями процессора. Немаловажная роль отведена UNB в операциях снижения мощности и изменения частоты памяти в зависимости от нагрузки, чтобы обеспечить оптимальное энергопотребление для каждого рабочего модуля.

Как и предшествующие APU, процессоры Trinity содержат по два 64-битных контроллера DDR3-памяти, поддерживающих модули памяти вплоть до DDR3-1866. Максимальный объем поддерживаемой памяти для десктопных процессоров Trinity составляет 64 Гбайт.

Ядро Piledriver

После краткого знакомства с семейством APU Triniry рассмотрим более детально микроархитектуру вычислительного ядра Piledriver.

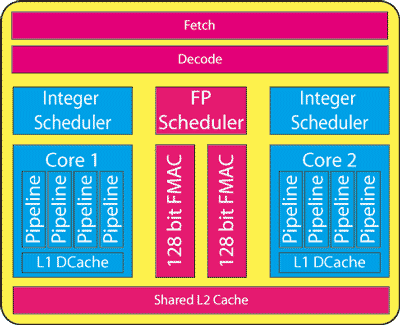

Как уже отмечалось, Piledriver — это улучшенный вариант процессорной микроархитектуры Bulldozer. Напомним, что ядро в микроархитектуре AMD Bulldozer и процессорные ядра в других микроархитектурах — это не одно и то же. Дело в том, что процессоры AMD на базе микроархитектуры AMD Bulldozer либо Piledriver предусматривают модульную архитектуру. Каждый модуль сам по себе (в терминологии компании AMD) является двухъядерным. К примеру, в четырехъядерном процессоре Triniry содержатся два двухъядерных модуля (рис. 2).

Рис. 2. Блок-схема двухъядерного модуля

в процессорной микроархитектуре

AMD Bulldozer/Piledriver

Однако то, что компания в данном случае называет ядром, на самом деле до настоящего процессорного ядра не дотягивает. Модуль, в котором расположены два ядра, вполне можно было бы назвать ядром, а сами ядра — вычислительными целочисленными кластерами. То есть, на наш взгляд, более корректно говорить не о модуле с двумя ядрами, а о ядре с двумя вычислительными кластерами.

Дело в том, что в каждом двухъядерном модуле AMD часть ресурсов выполнена разделяемой между обоими ядрами. Так, предпроцессор вместе с кэшем инструкций L1I разделяется между обоими ядрами, как и кэш L2. Особенностью модуля AMD также является то обстоятельство, что сами по себе ядра имеют лишь целочисленные исполнительные конвейеры, а для работы с вещественными данными используют разделяемый FP-кластер. То есть получается, что модуль в микроархитектуре AMD Bulldozer/Piledriver является как бы полутораядерным, но никак не двухъядерным. Вообще, по эффективности двухпоточной обработки данных модуль в микроархитектуре AMD Bulldozer/Piledriver превосходит одно процессорное ядро Intel с технологией Hyper-Threading, но уступает двум полноценным ядрам.

Теперь более подробно рассмотрим особенности вычислительного модуля процессора в микроархитектуре AMD Bulldozer/Piledriver.

Процесс выборки инструкций из кэша I-cache, их декодирования и продвижения к исполнительным блокам реализован на уровне всего процессорного модуля, то есть является разделяемым для двух вычислительных ядер.

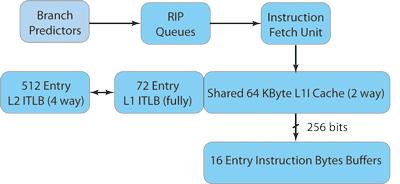

Для микроархитектур AMD Bulldozer/Piledriver размер кэша инструкций L1I составляет 64 Кбайт, причем сам кэш является двухканальным.

Выборка инструкций из кэша L1I производится на спекулятивной основе и с использованием блока предсказания ветвлений (Branch Predictors).

В микроархитектуре AMD Bulldozer/Piledriver блок предсказания ветвлений и переходов (Branch Predictors), как и другие элементы предпроцессора, является разделяемым между двумя ядрами процессорного модуля и отделен от модуля выбора инструкций (Instruction Fetch Unit) двумя буферами очередей предсказанных относительных указателей инструкций (Relative Instruction Pointers, RIP) — по одному RIP Queues на каждое ядро. Блок предсказания ветвлений и переходов может осуществлять упреждающие предсказания относительных указателей инструкций до тех пор, пока буферы очередей (RIP Queues) не заполнятся. Буфер ассоциативной трансляции использует его для доступа в L1I и ITLB. Напомним, что буфер ассоциативной трансляции (Translation Lookaside Buffer, TLB) выполняет трансляцию виртуальных адресов страниц памяти в физические. В микроархитектуре AMD Bulldozer применяется двухуровневая иерархия TLB-кэшей инструкций.

В микроархитектуре AMD Bulldozer ITLB-кэш первого уровня (L1) рассчитан на 72 записи, причем поддерживаются записи для различных страниц памяти (Small Page, Large Page). TLB-буфер второго уровня рассчитан на 512 записей, причем поддерживаются записи только для страниц памяти размером 4K (Small Page). Отметим, что кэш L1 ITLB является полностью ассоциативным, а кэш L2 ITLB — 4-канальным.

Что касается микроархитектуры AMD Piledriver, то данных относительно размеров TLB-кэшей первого и второго уровней у нас нет. Компания AMD лишь отмечает, что в новой микроархитектуре Piledriver улучшено предсказание ветвлений и переходов и используются TLB-кэши, рассчитанные на большее количество записей, нежели в микроархитектуре Bulldozer.

Напомним, что инструкции x86 имеют переменную длину, причем информация о длине инструкций сохраняется в специальных полях в кэше инструкций L1I. Загрузка инструкций переменной длины x86 из кэша L1I происходит блоками определенной длины, из которых в дальнейшем выделяются инструкции, подвергаемые декодированию.

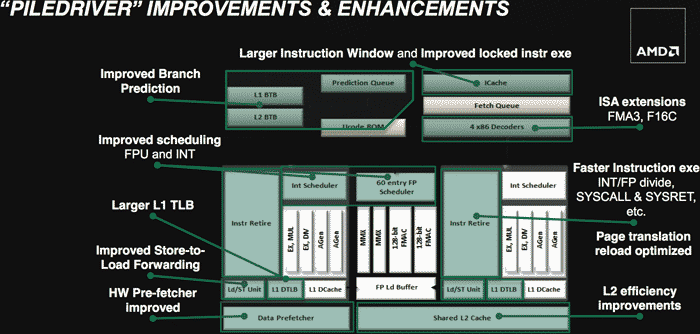

В микроархитектуре Bulldozer длина блока выборки составляет 32 байта (256 бит), что согласуется с возможностями декодера. О длине блока выборки в микроархитектуре Piledriver данных нет, но известно, что длина блока выборки стала больше (рис. 3)

Рис. 3. Сравнение микроархитектур Piledriver и Bulldozer

Выбранные блоками х86-инструкции поступают в буфер IBB (Instruction Byte Buffer). Собственно, таких IBB-буферов два — по одному на каждое ядро процессорного модуля.

После выборки инструкций x86 из кэша L1I наступает этап их декодирования (трансляции) в машинные команды. В терминологии AMD декодированные инструкции фиксированной длины называются макрооперациями (Macro-operations, Mops). Макрооперации могут включать одновременно как арифметические операции, так и операции с памятью. Такие макрооперации иногда называют сложными (complex ops, cops). Кроме макроопераций, которые содержат одновременно несколько действий, в микроархитектуре AMD рассматриваются микрооперации (uops). Разница между Mops и uops заключается в том, что uops может содержать только одну элементарную операцию (арифметическую операцию, операцию чтения или записи), а Mops содержит комбинацию нескольких элементарных операций.

В микроархитектуре AMD Bulldozer все x86-инструкции делятся на простые и сложные. Простые инструкции при декодировании транслируются в одну или две макрооперации (Mops), а сложные инструкции транслируются в более чем две макрооперации.

При декодировании простые инструкции отсылаются в аппаратный декодер, построенный на логических схемах и называемый DirectPath, а сложные — в микропрограммный (Microcode Engine) декодер, называемый VectorPath. Этот декодер представляет собой своеобразный программный процессор. Он содержит программный код, хранящийся в MIS (Microcode Instruction Sequencer), на основе которого воспроизводится последовательность макроопераций.

Аппаратный декодер DirectPath является четырехканальным и может декодировать за один такт четыре x86-инструкции, но так, чтобы скорость декодирования не превышала 4 Mops за такт.

При декодировании сложных инструкций с использованием декодера VectorPath работа декодера DirectPath блокируется, то есть сложные инструкции не могут декодироваться одновременно с простыми.

Макрооперации, полученные в результате декодирования инструкций, поступают в буфер Dispatch Group Buffers, где они объединяются в группы по 4 Mops.

После декодирования команды поступают в блок внеочередного выполнения команд (Out-of-Order). Первоначально происходит переименование и распределение дополнительных регистров процессора, которые не определены архитектурой набора команд. Переименование регистров позволяет добиться исполнения команд вне очереди. На следующем этапе осуществляется переупорядочение декодированных инструкций не в порядке их поступления (Out-of-Order) с тем, чтобы впоследствии можно было реализовать их более эффективное выполнение на исполнительных блоках.

Существует два подхода к организации внеочередного выполнения команд: с использованием буфера переупорядочения (ReOrder Buffer, ROB) и с применением физических регистровых файлов (Physical Register File, PRF).

При использовании ROB-буфера каждая декодированная инструкция имеет копию операнда или операндов, которые ей требуются. В случае применения физических регистровых файлов все операнды сохраняются именно в PRF. Это позволяет самим декодированным инструкциям сохранять лишь указатели на операнды, но не сами операнды. С одной стороны, такой подход позволяет снизить энергопотребление процессора, поскольку перемещение по конвейеру микроопераций вместе с их операндами требует существенных затрат энергопотребления, а с другой — использование физического регистрового файла позволяет сэкономить место на кристалле.

В микроархитектурах AMD Bulldozer/Piledriver для сохранения операндов применяются как раз физические регистровые файлы. Первоначально из буфера Dispatch Group Buffers группы по 4 Mops поступают в блок очереди отставки команд (Retirement Queue), где они переупорядочиваются. В микроархитектуре AMD Bulldozer блок очереди отставки команд рассчитан на 128 записей, а вот размер этого блока в микроархитектуре Piledriver не уточняется.

При этом все Mops содержат лишь указатели на операнды, которые сохраняются в PRF-файлах. В микроархитетуре AMD Bulldozer для целочисленных операций и операций для работы с памятью используется физический регистровый файл на 96 записей, который содержит все переименованные регистры. Для всех FP- и SIMD-макроопераций применяется отдельный регистровый файл на 160 записей. Опять же размеры регистровых файлов в микроархитектуре Piledriver не уточняются — отмечается лишь, что блок очереди отставки команд (Retirement Queue) в микроархитектуре Piledriver улучшен.

Напомним, что вычислительный кластер для работы с FP-данными является разделяемым между двумя ядрами. Соответственно как только в блоке очереди отставки операций (Retirement Queue) какого-либо ядра процессора встречается FP- или SIMD-макрооперация, она посылается на вычислительный FP-кластер, однако статус отставки этой операции отслеживается в целочисленном ядре в блоке Retirement Queue.

После того как все макрооперации переименованы, они направляются на планировщик инструкций (Scheduler). В целочисленном ядре планировщик инструкций является унифицированным, поскольку используется как для арифметических операций для работы с целочисленными данными, так и для операций с памятью. В разделяемом FP-кластере применяется свой планировщик инструкций на 60 записей. В планировщике макрооперации сохраняются до тех пор, пока для их исполнения не будут готовы все необходимые данные. Компания AMD отмечает, что и планировщик целочисленного ядра, и планировщик FP-кластера в микроархитектуре Piledriver стали лучше, но в чем заключается улучшение — не уточняется. Известно, что и размер планировщика FP-кластера не изменился — он рассчитан на 60 записей. А вот относительно размера планировщика целочисленного ядра в микроархитектуре Piledriver ясности нет. В микроархитектуре Bulldozer этот планировщик рассчитан на 40 записей.

После того как все макрооперации прошли диспетчеризацию и переупорядочение в соответствующих планировщиках, они могут быть выполнены в соответствующих исполнительных устройствах. Сами исполнительные устройства в микроархитектуре Piledriver изменений не претерпели.

Блок операций с целыми числами состоит из четырех функциональных устройств: двух устройств для работы с адресами памяти (AGU0 и AGU1) и двух устройств для выполнения арифметических операций (ALU0 и ALU1). По мере готовности данных планировщик может запускать на исполнение из каждой очереди одну целочисленную операцию в устройство ALU и одну адресную операцию в устройство AGU. Количество одновременных обращений к памяти не должно превышать двух.

Разделяемый FP-кластер содержит четыре исполнительных устройства. Причем все исполнительные устройства являются 128-битными. Это особенно важно отметить с учетом того обстоятельства, что процессоры на базе микроархитектуры AMD Bulldozer/Piledriver поддерживают выполнение 256-битных AVX-инструкций. Каждая AVX-инструкция декодируется как два 128-битных Mops.

Как уже отмечалось, для работы с памятью (операции чтения и записи) в микроархитектуре AMD Bulldozer предусмотрено по два исполнительных устройства AGU в каждом ядре процессорного модуля. Каждое устройство AGU связано с буфером загрузки (Load queue) и буфером записи (Store queue), которые, в свою очередь, связаны уже с кэшем данных L1D.

В микроархитектуре AMD Bulldozer для трансляции логических адресов памяти в физические используется кэш L1 DTLB, рассчитанный на 32 записи. В случае промаха в кэше L1 DTLB данные запрашиваются в кэше L2 DTLB, который уже рассчитан на 1024 записи. В случае микроархитектуры Piledriver работает такая же схема, однако размеры кэшей L1 DTLB и L2 DTLB не уточняются.

Теоретически кэш L1D может за один такт выдавать два 128-битных значения (операции Load) и записывать (операции Store) одно 128-битное значение, то есть имеет пропускную способность 48 байт за такт. Однако наличие лишь двух AGU не позволяет осуществлять три одновременных обращения к кэшу L1D.

Подробная структурная схема двухъядерного модуля Piledriver приведена на рис. 4.

Рис. 4. Структурная схема двухъядерного модуля Piledriver

Одним из нововведений микроархитектуры Piledriver стало обновление архитектуры набора команд (ISA) новыми инструкциями: FMA3 и F16C в дополнение к AVX, AVX 1.1 и AES.

Графическое ядро в APU Trinity

В APU Trinity используется графическое ядро на основе архитектуры Cayman, которое, как уже отмечалось, имеет кодовое название Northern Islands. Если кратко, то это графическое ядро основано на дизайне VLIW4 и для старших моделей процессоров содержит шесть SIMD-движков, в каждом из которых имеется по 16 VLIW4-блоков (Stream Processing Untits, SPU), то есть в сумме получаем 384 вычислительных потоковых ядра.

Кроме потоковых процессоров, графический процессор Northern Islands включает 24 текстурных блока (по четыре TMU на каждый SIMD) и восемь блоков ROP (рис. 5).

Рис. 5. Структурная схема графического процессора

Northern Islands

Напомним, что архитектура Cayman используется в графических процессорах AMD Radeon HD 6900, которые были анонсированы компанией в 2011 году. Тут важно акцентировать внимание на том обстоятельстве, что Northern Islands — это не новая архитектура Graphics Core Next (GCN), которая лежит в основе графического процессора AMD Radeon HD 7970, а архитектура предыдущего поколения.

Вкратце напомним, что подразумевается под архитектурой VLIW4.

Одним из революционных моментов в архитектуре графических процессоров стал в свое время переход на унифицированные шейдерные процессоры. Компания ATI, которая теперь принадлежит AMD, осуществила этот переход в процессорах ATI Radeon HD серии 2000.

Важно также, что унифицированные шейдерные процессоры представляли собой суперскалярные процессоры общего назначения для обработки данных с плавающей запятой. Напомним, что традиционно в процессорах задействуются два типа математики: векторная и скалярная.

До появления графического процессора ATI Radeon HD серии 2000 на базе новой архитектуры унифицированных шейдерных процессоров векторная архитектура являлась в какойто мере традиционной для графических процессоров, то есть в графических процессорах предыдущего поколения применялась векторная архитектура исполнительных блоков.

В графических процессорах ATI Radeon HD серии 2000 отказались от традиционной векторной архитектуры исполнительных блоков и перешли к суперскалярной архитектуре на базе суперскалярных потоковых процессоров (Stream Processing Untits, SPU). SPU группируются в блоки, называемые SIMD Engine или SIMD Core.

Говоря об архитектуре графических процессоров на основе скалярных унифицированных шейдерных процессоров, немаловажно отметить, что в них использовался так называемый VLIW-дизайн. Собственно, понятия суперскалярности исполнительных блоков процессора и VLIW-архитектуры тесно взаимосвязаны. Действительно, суперскалярность исполнительных блоков означает, что они могут параллельно выполнять несколько инструкций из одного потока. Однако для того, чтобы такое одновременное выполнение инструкций было возможно, необходимо, чтобы они были независимы друг от друга. В центральных процессорах для того, чтобы было возможно параллельное выполнение инструкций, используются специальные блоки внеочередного выполнения команд (out-of-order), которые переупорядочивают инструкции не в порядке их поступления для того, чтобы выделить из них те инструкции, которые можно выполнять параллельно, тем самым максимально загрузив исполнительные блоки процессора. Однако такое переупорядочение инструкций «на лету» — довольно сложная техническая задача, а блоки предсказания и внеочередного выполнения команд занимают значительную часть кристалла процессора. В графических процессорах стали использовать несколько иной подход, когда переупорядочение инструкций для их параллельного исполнения происходит на этапе компиляции кода. То есть на этапе компиляции выделяются независимые инструкции, которые можно выполнять параллельно, и из этих независимых инструкций формируются длинные составные конструкции, называемые VLIW-инструкциями (Very Long Instruction Word).

В графических процессорах ATI Radeon HD серии 2000 каждый SPU, как уже отмечалось, наделен пятью ALU. Cоответственно в одной VLIW-инструкции может быть упаковано до пяти скалярных операций, что соответствует пяти ALU внутри одного SPU. Именно поэтому данная архитектура получила название VLIW5.

В процессорах Radeon HD серии 6000 (кодовое наименование Cayman) также применяется VLIW-архитектура, но SPU этих процессоров содержат всего четыре исполнительных блока.

Дело в том, что внутренние исследования компании AMD показали, что в современных играх при использовании VLIW-архитектуры эффективно применяются в среднем только 3,4 исполнительных блока в SPU, то есть в среднем в одну VLIW-инструкцию удается запаковать 3,4 инструкции. А потому в процессоре Cayman количество исполнительных блоков было снижено до четырех. Соответственно в одной VLIW-инструкции может быть упаковано вплоть до четырех скалярных операций, а сама архитектура процессора стала называться VLIW4.

Все графические процессоры архитектурно устроены таким образом, чтобы обрабатывать одновременно множество потоков инструкций (нитей), количество которых может исчисляться тысячами. Собственно, в этом заключается главная особенность графических процессоров — возможность параллельной обработки огромного множества программных нитей. Однако эффективная обработка таких нитей возможна только в том случае, если все нити графической программы, осуществляя параллельную обработку данных, в целом движутся параллельным курсом по коду программы, причем для всех нитей в конкретный момент времени реализуется одна и та же операция, но с разными данными. Так вот, графические процессоры AMD с VLIW-дизайном устроены таким образом, что каждый мини-процессор (SIMD Engine) может выполнять только одну операцию (инструкцию с одним программным адресом), но с разными операндами. Таким образом, все 16 SPU в блоке SIMD Engine процессора Cayman выполняют одну и ту же инструкцию. Например, это может быть инструкция сложения содержимого двух регистров: она одновременно выполняется всеми SPU блока SIMD Engine, но регистры берутся разные. Собственно, отсюда и название SIMD (Single Instruction, Multiple Data — одна инструкция, множество данных).

Напомним, что каждый SPU содержит четыре исполнительных блока (ALU), что позволяет каждому SPU одновременно обрабатывать четыре нити инструкций.

Идеальной является ситуация, когда все нити выполняются параллельно (синхронно), то есть во всех нитях исполняется одна и та же инструкция.

Если же в результате ветвления в программе нити расходятся в своем пути исполнения кода, то происходит так называемая сериализация. В этом случае используются не все исполнительные блоки в SIMD Engine, поскольку нити подают на исполнение различные инструкции, а SIMD Engine может исполнять только инструкцию с одним адресом. Естественно, в этом случае производительность снижается. Если происходит сериализация нитей, то, образно говоря, нужные нити подтормаживаются при выполнении до выравнивания всех нитей по номеру инструкции.

Итак, в APU Trinity используется графическое ядро дизайна VLIW4, то есть каждый SPU содержит четыре исполнительных блока (ALU). Все SPU объединены группами по 16 штук в шесть SIMD-движков.

Если говорить о других особенностях графического ядра в APU Trinity, то стоит отметить поддержку всех известных типов полноэкранного сглаживания, в том числе SSAA, EQAA и MLAA. Естественно, графическое ядро поддерживает DirectX 11 и OpenCL 1.1.

Несмотря на то обстоятельство, что графическое ядро в процессоре Trinity основано на архитектуре предыдущего поколения, блок кодирования видео (UVD) был позаимствован у более поздней архитектуры Graphics Core Next (графический процессор AMD Radeon HD 7970).

UVD третьего поколения отличается поддержкой аппаратной обработки формата MPEG-4/ DivX, а также возможностью декодирования двух каналов видео в формате Full HD, что используется при декодировании видеоданных в стереоформате.

Кроме того, стоит отметить технологию улучшения качества проигрывания потокового видео — AMD Quick Stream Technology, а также технологию стабилизации видеоизображения в реальном времени AMD Steady Video 2.0.

Технология AMD Steady Video 2.0 предназначена для улучшения видеороликов плохого качества, снятых с рук, без использования штатива и других аналогичных средств для стабилизации изображения.

Графические ядра с поддержкой Steady Video 2.0 способны обрабатывать случайные сдвиги с амплитудой до 32 пикселов в любом направлении, и для этого требуется поддержка специализированных команд, которая теперь есть и в последнем поколении APU.

Модели процессоров

В настоящее время компания AMD представила шесть моделей настольных APU Trinity: серии A10, A8, A6 и A4 (табл. 1). APU серий A10 и A8 являются четырехъядерными (c двумя двухъядерными модулями), и кэш L2 этих APU составляет 4 Мбайт (по 2 Мбайт на каждый двухъядерный модуль).

APU серий A6 и A4 двухъядерные, а их кэш L2 равен 2 Мбайт.

Разница между APU серий A8 и A10 заключается в версии графического ядра. Так, в APU серии A10 используется графическое ядро Radeon HD 7660D, содержащее 384 потоковых ядра (шесть SIMD-движков по 16 SPU в каждом), а в APU серии A8 — графическое ядро Radeon HD 7560D, содержащие 256 потоковых ядер (четыре SIMD-движка).

В топовой модели A10-5800К графическое ядро работает на частоте 800 МГц, а в остальных APOU серий A10 и A8 — на частоте 760 МГц.

В APU серии A6 используется графическое ядро Radeon HD 7540D, содержащие 192 потоковых ядра (три SIMD-движка), а в APU серии A4 — графическое ядро Radeon HD 7480D, содержащие 128 потоковых ядер (два SIMD-движка).

Модели APU с литерой «К» имеют разблокированный коэффициент умножения.

Ну и, естественно, модели APU отличаются друг от друга своей номинальной тактовой частотой и частотой в режиме Turbo Core.

Чипсет AMD A85X FCH

Одновременно с APU семейства Trinity компания AMD представила и новый чипсет A85X FCH, который заменяет собой чипсет AMD A75. Отметим тем не менее, что формально процессоры Trinity совместимы и с чипсетом A75 и тут уж всё зависит от производителя материнской платы.

Однокристальный чипсет AMD A85X имеет встроенный контроллер PCI Express 2.0 (GPP) на четыре линии. Эти линии не могут служить для организации слота PCI Express для дискретной графики, но могут использоваться для интегрированных контроллеров и создания слотов для карт расширения.

Кроме того, чипсет AMD A85X нативно поддерживает шину PCI, а для связи с процессором используется шина UMI (Unified Media Interface) с пропускной способностью 2 Гбайт/с в каждом направлении (в основе этой шины лежат четыре линии PCI Express 2.0).

Чипсет AMD A85X поддерживает восемь портов SATA 6 Гбит/с с возможностью организации RAID-массивов уровней 0, 1, 5 и 10, четыре порта USB 3.0, десять портов USB 2.0 и два порта USB 1.1.

Вообще, если сравнивать чипсеты AMD A85X и A75, то нужно сказать, что различий у них немного. По большому счету, увеличилось лишь количество портов SATA 6 Гбит/c (в чипсете A75 их было шесть), но вряд ли это можно считать преимуществом. Действительно, мощную RAID-систему два дополнительных порта создать не позволят, поскольку узким местом в данном случае станет UMI-шина с пропускной способностью 2 Гбайт/с в одном направлении (16 Гбит/с).

Методика тестирования

Итак, после краткого обзора APU Trinity можно перейти к рассмотрению результатов его тестирования. Напомним, что мы тестировали топовый десктопный процессор A10-5800K.

Тестирование мы разделили на два этапа. На первом этапе оценивалась интегральная производительность APU Trinity при работе с различными пользовательскими приложениями, а на втором — производительность интегрированного графического ядра в играх.

Понятно, что результаты тестирования процессора (время выполнения им тестовых задач) интересны не сами по себе, а в сравнении с чемлибо. Для сравнения мы взяли процессор Intel Core i7-3770K, который традиционно используется нами для получения референсных результатов.

Понятно, что сопоставлять результаты тестирования процессора AMD A10-5800K с результатами процессора Intel Core i7-3770K не очень корректно, поскольку они находятся в разных ценовых категориях. Так, рекомендованная цена процессора AMD A10-5800K составляет 160 долл., а процессора Intel Core i7-3770K — 332 долл., то есть она в два с лишним раза выше. Вообще, если исходить из стоимости, то конкурентом топового процессора AMD A10-5800K являются бюджетные варианты процессоров семейства Intel Core i3 и некоторые модели процессоров семейства Intel Core i5. Однако на момент тестирования в нашем распоряжении не оказалось бюджетных вариантов процессоров Intel.

Тем не менее даже сопоставление результатов тестирования процессоров Intel Core i7-3770K и AMD A10-5800K позволяет сделать выводы относительно возможностей процессора AMD A10-5800K.

Для оценки интегральной производительности процессоров при работе с различными пользовательскими приложениями мы применяли наш тестовый скрипт ComputerPress Benchmark Script 11.0, который подробно описан в сентябрьском номере журнала КомпьютерПресс.

Для оценки производительности встроенного в процессор графического ядра в играх мы использовали скрипт ComputerPress Game Benchmark Script v.6.0, подробное описание которого приводится в статье «Новый игровой бенчмарк ComputerPress Game Benchmark Script v.6.0», опубликованной в КомпьютерПресс № 02’2011. Во всех играх и игровых бенчмарках устанавливалось разрешение 1920×1080 и тестирование проводилась при настройках на максимальное качество отображения и максимальную производительность (минимальное качество).

Стенд для тестирования процессора AMD A10-5800K имел следующую конфигурацию:

- системная плата — GIGABYTE GA-F2A85X-UD4;

- чипсет системной платы — AMD A85X;

- видеокарта — встроенное в процессор графическое ядро (Radeon HD 7660D);

- память — Kingston HyperX Predator DDR3-2666;

- объем памяти — 8 Гбайт (два модуля по 4 Гбайт);

- режим работы памяти — DDR3-1866, двухканальный;

- накопитель — Intel SSD 520 Series (240 Гбайт);

- операционная система — Microsoft Windows 7 Ultimate (32-bit).

Для тестирования процессора Intel Core i7-3770K использовался стенд следующей конфигурации:

- системная плата — ASUS P8Z77 V PRO;

- чипсет системной платы — Intel Z77 Express;

- видеокарта — встроенное в процессор графическое ядро (Intel HD 4000);

- память — Kingston HyperX Predator DDR3-2666;

- объем памяти — 8 Гбайт (два модуля по 4 Гбайт);

- режим работы памяти — DDR3-1600, двухканальный;

- накопитель — Intel SSD 520 Series (240 Гбайт);

- операционная система — Microsoft Windows 7 Ultimate (32-bit).

Результаты тестирования

Подробные результаты тестирования процессоров с применением скрипта ComputerPress Benchmark Script v. 11.0 представлены в табл. 2, а скрипта ComputerPress Game Benchmark Script v.6.0 — в табл. 3.

Как видно по результатам теста ComputerPress Benchmark Script v. 11.0, производительность топового процессора семейства Trinity (A10-5800K) в 1,7 раза ниже производительности топового процессора семейства Ivy Bridge (Core i7-3700K). Но еще раз напомним, что стоимость процессора Core i7-3700K в 2,7 раза выше стоимости процессора A10-5800K.

До сих пор мы рассматривали лишь вычислительные возможности процессоров, без учета возможностей интегрированных графических ядер.

Итак, в плане вычислительной производительности процессора AMD A10-5800K всё понятно. Этот топовый процессор семейства Trinity может конкурировать по производительности лишь с младшими моделями семейства Ivy Bridge, то есть с процессорами серии Intel Core i3 третьего поколения. Одним словом, AMD A10-5800K — это бюджетный процессор, нацеленный на компьютеры начального уровня.

Впрочем, выносить окончательный вердикт, пожалуй, рано. Ведь мы еще не проанализировали производительность интегрированного графического ядра в играх. Может, именно здесь процессор AMD обойдет процессор Intel по полной программе и реабилитирует себя. Что ж, обратимся к результатам тестирования процессоров в играх.

Как видно по результатам тестирования (см. табл. 3), при настройках на максимальное качество в некоторых играх явное преимущество (почти вдвое) на стороне графического ядра Radeon HD 7660D процессора AMD A10-5800K. Есть игры, где возможности графических ядер Intel HD 4000 и Radeon HD 7660D примерно одинаковые, а есть игры, где незначительное преимущество имеет графическое ядро Intel HD 4000. В целом же, если говорить о неком интегральном результате, который можно определить как среднегеометрическое от результатов во всех играх, процессор AMD A10-5800K показывает в играх на 25% более высокий результат, чем процессор Intel Core i7-3700K. Еще раз подчеркнем, что речь идет о настройках игр на максимальное качество при разрешении 1920×1080.

При настройках на максимальную производительность (за счет ухудшения качества отображения) лидерство во всех играх на стороне процессора AMD A10-5800K. И если ориентироваться на интегральный результат, то AMD A10-5800K опережает Intel Core i7-3700K примерно на 27%.

Обобщая результаты тестирования процессоров Intel Core i7-3700K и AMD A10-5800K в играх, нужно отметить одно важное обстоятельство. При настройках игр на максимальное качество ни один из них не позволяет получить приемлемый для комфортной игры результат. Напомним, что если результат составляет менее 40 fps, то игра считается некомфортной.

И даже при настройках на минимальное качество имеется лишь несколько игр, в которых результат выше 40 fps. Причем это верно как для процессора AMD A10-5800K, так и для процессора Intel Core i7-3700K.

Таким образом, можно утверждать, что, несмотря на свое 25-27-процентное преимущество в производительности, графическое ядро процессора AMD A10-5800K всё равно не позволит комфортно играть в современные динамичные 3D-игры и не может рассматриваться как основа для игрового ПК.

То есть, действительно, графическое ядро процессора AMD A10-5800K примерно на 26% производительнее графического ядра процессора Intel Core i7-3700K. Но что делать с этими 26% — не очень понятно. По сути, от этого преимущества нет никакого толку.

Заключение

К нашему большому сожалению, компания AMD перестала конкурировать с Intel в сегменте производительных процессоров и сконцентрировалась на производстве бюджетных процессоров начального уровня.

Почему к сожалению? Да потому, что отсутствие конкуренции обычно заканчивается очень плохо. Если раньше компания AMD выступала в качестве стимулирующего (в плане производства хороших процессоров) и сдерживающего (в плане стоимости) факторов, то теперь таких стимулирующих и сдерживающих факторов у Intel просто нет. И чем всё это кончится, пока неясно.

Что же касается процессора AMD A10-5800K, то его можно рассматривать лишь в качестве основы для бюджетных домашних ПК начального и среднего уровней или офисных ПК. Процессоры этого семейства могут конкурировать по производительности лишь с младшими моделями процессоров Intel (серия процессоров Intel Core i3 третьего поколения), ну а топовому процессору Intel Core i7-3770K топовый процессор AMD A10-5800K сильно проигрывает в производительности.

Интегрированное в процессор AMD A10-5800K графическое ядро не может рассматриваться в качестве основы для игровых решений, а поддержка DirectX 11 фактически не оправдывает себя.