По следам IFD 2012: процессорная микроархитектура Intel Haswell

Графическое ядро в микроархитектуре Haswell

В рамках прошедшего форума IDF 2012 компания Intel впервые огласила информацию о новой процессорной микроархитектуре, известной под кодовым наименованием Haswell, которая станет основой для процессоров Intel Core четвертого поколения. Конечно же, далеко не все подробности стали достоянием гласности и на сегодняшний момент больше вопросов, чем ответов. Но это всё равно лучше, чем ничего. Итак, давайте поближе познакомимся с новой процессорной микроархитектурой Haswell.

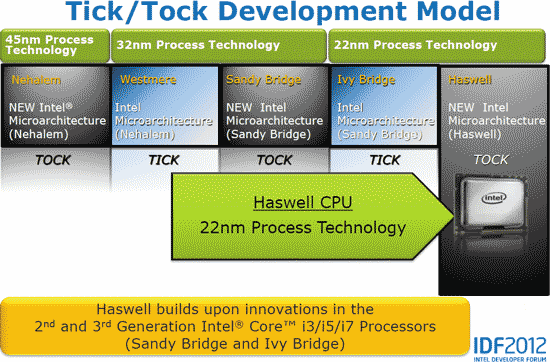

Вот уже в течение многих лет выход новых поколений процессоров Intel подчиняется эмпирическому правилу TICK-TOCK («тиктак»), суть которого заключается в том, что перевод производства на новый технологический процесс (TICK) и внедрение новой процессорной микроархитектуры (TOCK) происходит поочередно, с периодичностью примерно в два года. Например, если в первый год происходит переход на новый техпроцесс производства, то на второй год на этом же техпроцессе внедряется новая процессорная микроархитектура. На следующий год происходит перенос микроархитектуры на новый техпроцесс производства.

В частности, в конце 2011 года компания Intel выпустила 32-нм процессоры Sandy Bridge на базе новой процессорной микроархитектуры (цикл TOCK). Соответственно в 2012 году компания выпустила уже 22-нм версию процессоров на базе микроархитектуры Sandy Bridge, которые известны под кодовым наименованием Ivy Bridge (цикл TICK). Ну а в следующем году будут выпущены 22-нм процессоры на базе новой процессорной микроархитектуры Haswell.

Таким образом, Haswell — это 22-нм процессоры на новой микроархитектуре. Напомним, что в свое время процессорная микроархитектура Sandy Bridge была в какойто мере революционной, поскольку существенно отличалась от микроархитектуры Nehalem. Микроархитектуру Haswell в этом смысле назвать революционной нельзя. Она, скорее, представляет собой улучшенный вариант Sandy Bridge. Собственно, такое решение компании вполне логично. Архитектура Sandy Bridge оказалась очень удачной и кардинальным образом изменять ее просто нелогично. А вот провести тюнинг Sandy Bridge — это как раз то, что нужно.

Эмпирическое правило TICK-TOCK производства процессоров Intel

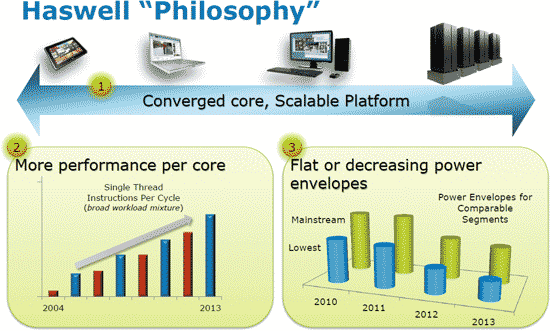

Основной акцент в микроархитектуре Haswell был сделан на энергопотребление, масштабируемость и производительность, ну а «философия» новой микроархитектуры заключается в том, что на ее основе будут производиться процессоры и для серверов, и для настольных ПК, и для ноутбуков/ультрабуков, и для планшетов.

То есть будут существовать процессоры Haswell с двумя, четырьмя ядрами и более (в случае серверных процессоров) и тремя вариантами графического ядра, которые пока условно обозначаются как GT1, GT2 и GT3.

Процессоры Haswell, так же как и процессоры Ivy Bridge, будут иметь PCI Express 3.0, но вот сколько именно линий PCI Express 3.0 будут поддерживать новые процессоры, пока не сообщается. Неизвестны и подробности о контроллере памяти, то есть пока нет официальной информации, касающейся количества каналов памяти (хотя разумно было бы предположить, что контроллер памяти DDR3 будет двухканальным), а также максимальной частоты памяти.

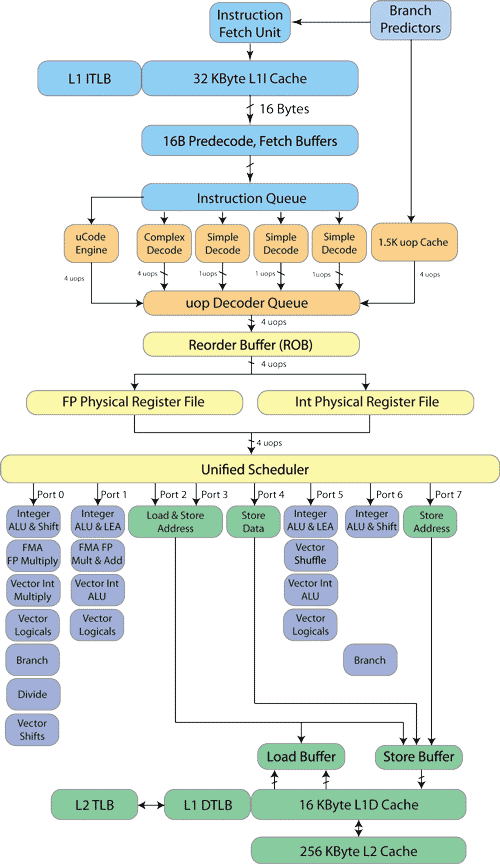

Вычислительное ядро Haswell

Как уже отмечалось, вычислительное ядро Haswell не претерпело кардинальных изменений в сравнении с вычислительным ядром Ivy Bridge — речь идет лишь об улучшении отдельных блоков ядра процессора. А потому уместным будет напомнить в общих чертах микроархитектуру ядра Ivy Bridge и остановиться на внесенных изменениях.

Итак, при работе вычислительного ядра Ivy Bridge инструкции x86 выбираются из кэша инструкций L1I (Instruction Сache) размером 32 Кбайт (кэш 8-канальный). В ядре Haswell кэш инструкций L1I не претерпел изменений: он имеет размер 32 Кбайт и является 8-канальным.

В ядре Ivy Bridge команды загружают 16-байтными блоками, то есть за каждый такт из кэша загружается 16-байтный блок команд. В ядре Haswell опять-таки команды загружаются 16-байтными блоками. Поскольку инструкции x86 имеют переменную длину, а длина блоков, которыми команды загружаются из кэша, фиксированная, при декодировании команд следует определить границы между отдельными командами. Информация о размерах команд хранится в кэше инструкций L1I в специальных полях (по 3 бита информации на каждый байт инструкций), а сама процедура выделения команд из выбранного блока называется предварительным декодированием (PreDecode). В принципе, информацию для определения границ команд можно было бы использовать в самом декодере непосредственно в процессе декодирования команд. Однако это неизбежно отразилось бы на скорости декодирования, да и невозможно было бы декодировать одновременно несколько команд. Процедура предварительного декодирования позволяет поддерживать постоянный темп декодирования независимо от длины и структуры команд.

«Философия» микроархитектуры Haswell

После операции выборки команды организуются в очередь (Instruction Queue), а затем передаются в декодер. При декодировании (Decode) команды преобразуются в машинные микрооперации (обозначаются как micro-ops или uOps).

Декодер ядра процессора с микроархитектурами Ivy Bridge и Haswell является четырехканальным и может декодировать в каждом такте до четырех инструкций x86. В принципе, длина одной команды может достигать 16 байт, однако средняя длина команд составляет 4 байта. Поэтому в среднем в каждом 16-байтном блоке загружается четыре команды, которые при использовании четырехканального декодера одновременно декодируются за один такт. Однако существуют команды длиннее 4 байт и при загрузке нескольких таких команд в одном блоке эффективность декодирования снижается.

Четырехканальный декодер состоит из трех простых декодеров, декодирующих простые инструкции в одну микрооперацию, и одного сложного, который способен декодировать одну инструкцию в четыре микрооперации (декодер типа 4-1-1-1). Для еще более сложных инструкций, декодирующихся более чем в четыре микрооперации, сложный декодер соединен с блоком uCode Sequenser, который и применяется для декодирования подобных инструкций.

При декодировании инструкций используются технологии Macro-Fusion и Micro-Fusion.

Macro-Fusion — это слияние двух x86-инструкций в одну сложную микрооперацию micro-ops, которая в дальнейшем будет выполняться именно как одна микрооперация. Естественно, такому слиянию могут подвергаться не любые инструкции, а только некоторые пары инструкций (например, инструкция сравнения и условного перехода). Без применения технологии Macro-Fusion за каждый такт процессора могут декодироваться только четыре инструкции (в четырехканальном декодере), а при использовании технологии Macro-Fusion в каждом такте могут считываться пять инструкций, которые преобразуются в четыре за счет слияния и подвергаются декодированию.

Отметим, что для эффективного поддержания технологии Macro-Fusion применяются расширенные блоки ALU (Arithmetical Logic Unit), которые способны поддержать выполнение слитых микроопераций.

Технология Macro-Fusion использовалась еще в микроархитектуре Intel Core, однако в каждой последующей микроархитектуре расширялся набор x86-инструкций, для которого возможно слияние в одну микрооперацию. Кроме того, первоначально технология Macro-Fusion реализовывалась только в 32-битном режиме. Начиная с микроархитектуры Nehalem слияние x86-инструкций стало поддерживаться и для 64-битного режима работы процессора.

В отношении расширения набора инструкций в микроархитектуре Haswell, для которого возможно слияние, по сравнению с микроархитектурой Sandy Bridge данных пока нет, но, скорее всего, этот набор инструкций не изменился.

Micro-Fusion — это слияние двух микроопераций (не x86-инструкций, а именно микроопераций) в одну, содержащую два элементарных действия. В дальнейшем две такие слитые микрооперации обрабатываются как одна, что в результате позволяет снизить количество обрабатываемых микроопераций и тем самым увеличить общее количество исполняемых процессором инструкций за один такт. Понятно, что операция слияния двух микроопераций возможна далеко не для всех пар микроопераций. И опять-таки, пока нет данных, расширился ли набор микроопераций, для которых возможна операция Micro-Fusion, в микроархитектуре Haswell.

Блок-схема ядра Haswell

Говоря о процедуре выборки программных инструкций, необходимо также отметить наличие блока обнаружения программных циклов Loop Stream Detector (LSD), который принимает непосредственное участие в процессе выборки инструкций и позволяет избежать повторов в выполнении одних и тех же операций. В ядре на базе микроархитектуры Ivy Bridge LSD блок расположен за декодером и рассчитан на 28 декодированных инструкций. В ядре на базе микроархитектуры Ivy Bridge блок LSD, естественно, также присутствует, но точных данных, на сколько декодированных инструкций он рассчитан, пока нет. Скорее всего, как и остальные функциональные блоки предпроцессора, LSD-блок не поменялся.

Поскольку LSD хранит уже декодированные инструкции, при обнаружении программных циклов инструкции в цикле пропускают фазы выборки (Fetch), предсказания ветвлений в программе (Branch Prediction) и декодирования, а сами команды генерируются и поступают в декодер непосредственно из буфера LSD. Это позволяет, с одной стороны, снизить энергопотребление ядра процессора, а с другой стороны, обойти фазу выборки команд (фактически, на время выполнения программного цикла отключается предпроцессор процессора).

Кроме того, в микроархитектуре Haswell и Ivy Bridge применяется также кэш декодированных микроопераций (Decoded Uop Cache), в который поступают все декодированные микрооперации. В микроархитектуре Ivy Bridge этот кэш рассчитан приблизительно на 1500 микроопераций средней длины. Точных данных относительно размера Decoded Uop Cache в микроархитектуре Haswell у нас нет, но, по всей видимости, он также не поменялся.

Концепция кэша декодированных микроопераций заключается в том, чтобы сохранять в этом кэше уже декодированные последовательности микроопераций. В результате, если нужно выполнить некую x86-инструкцию повторно, а соответствующая ей последовательность декодированных микроопераций все еще находится в кэше декодированных микроопераций, нет необходимости вторично выбирать эту инструкцию из кэша L1 и декодировать ее — уже декодированные микрооперации поступают из кэша на дальнейшую обработку.

Эффективность применения кэша декодированных микроопераций во многом зависит от эффективности блока предсказания ветвлений (Branch Prediction Unit, BPU), который используется во всех современных процессорах.

Чтобы понять, почему блок предсказания ветвлений столь важен в процессоре и как он влияет на производительность, напомним, что фактически в любой болееменее сложной программе присутствуют команды условного перехода. Команда такого условного перехода означает следующее: если некоторое условие верно, то нужно перейти к выполнению программы, начиная с такого-то адреса, а если нет, то с другого. С точки зрения процессора команда условного перехода является своеобразным камнем преткновения. Действительно, ведь до тех пор, пока не выяснится, верно ли условие перехода, процессор не знает, какую часть программного кода исполнять далее, а следовательно, вынужден простаивать. Во избежание этого негативного явления как раз и используется блок предсказания ветвлений, который пытается угадать, на какой участок программного кода укажет команда условного перехода, еще до того, как она будет исполнена. На основе предсказания ветвлений производится выборка соответствующих 86-инструкций из кэша L1 или же из кэша декодированных микроопераций.

Когда команда условного перехода встречается в первый раз, то применяется так называемое статическое предсказание. Посути, BPU просто угадывает, какая программная ветвь будет выполняться далее. Причем в основе статического предсказания лежит предположение, что большинство обратных ветвлений происходит в повторяющихся циклах, когда инструкция ветвления используется для определения продолжения цикла или выхода из него. Чаще всего цикл продолжается, так что процессор будет снова повторно выполнять код цикла. По этой причине статическое предсказание считает, что все обратные ветвления всегда выполняются.

По мере того, как накапливается статистика результатов различных условных переходов (предыстория условных переходов), задействуется алгоритм динамического предсказания ветвлений, основанный как раз на анализе статистики результатов условных переходов, совершенных ранее. В алгоритмах динамического предсказания ветвлений используются таблица хранения истории предсказаний ветвлений (Branch History Table, BHT) и таблица хранения адресов инструкций (Branch Target Buffer, BTB). В эти таблицы записывается информация о результатах уже выполненных ветвлений. В BHT содержатся все условные переходы за несколько последних циклов. Кроме того, здесь хранятся биты, показывающие вероятность повторного выбора той же самой ветви. Биты расставляются на основании статистики предыдущих переходов. В стандартной бимодальной (2-битной) схеме существует четыре вероятности: ветвь часто выполняется (strongly taken), ветвь выполняется (taken), ветвь не выполняется (not taken), и ветвь часто не выполняется (strongly not taken).

Для того чтобы вынести решение о спекулятивном выполнении ветви, устройство должно знать точное местоположение кода в кэше L1 по направлению ветвления (назовем его целью ветвления). Цели уже выполненных ветвлений хранятся в BTB. Когда выполняется ветвление, BPU просто берет цель ветвления из таблицы и указывает предпроцессору начать выборку инструкций по этому адресу.

Понятно, что достоверность предсказания перехода зависит от размера BHT- и BTB-таблиц. Чем больше записей в этих таблицах, тем выше достоверность предсказания.

Следует отметить, что вероятность правильного предсказания ветвлений в современных процессорах очень высока (порядка 97-99%) и борьба фактически идет уже за доли процента.

Изменился ли блок BPU в микроархитектуре Haswell в сравнении с микроархитектурой Ivy Bridge, пока непонятно.

Как видим, предпроцессор ядра процессора Haswell не претерпел изменений в сравнении с предпроцессором ядра процессора Ivy Bridge. Незначительные изменения (типа расширения набора команд и микрооперация, для которых возможны операции слияния, и пр.) возможны, но официальных данных на этот счет пока нет.

После процесса декодирования x86-инструкций начинается этап их исполнения. Первоначально декодированные инструкции по четыре штуки за такт поступают в буфер Decoder Queue (встречаются также названия uop Allocation, Allocation Queue), и происходит переименование и распределение дополнительных регистров процессора (блок Allocate/Rename/ Retirement), которые не определены архитектурой набора команд. Переименование регистров позволяет добиться исполнения команд вне очереди, а следовательно, снизить простои процессора.

Идея переименования регистров заключается в следующем. В архитектуре x86 количество регистров общего назначения сравнительно невелико: доступно восемь регистров в 32-битном режиме, и 16 регистров в 64-битном. Представим, что исполняемая команда дожидается загрузки значений операндов в регистр из памяти. Данная операция длится долго, и хорошо бы на это время позволить использовать этот регистр для другой команды, операнды которой находятся ближе (например, в кэше первого уровня). Для этого временно переименовывается «ждущий» регистр и отслеживается история переименования. А «готовому к работе» регистру присваивается стандартное имя, чтобы снабженную операндами команду исполнить прямо сейчас. А когда придут данные из памяти, обращаются к истории переименования и возвращают изначальному регистру его законное имя. Иными словами, техника переименования регистров позволяет сократить простои, а ведение истории переименования помогает нивелировать конфликты.

В микроархитектуре Ivy Bridge буфер Decoder Queue рассчитан на 28 микроопераций, а в микроархитектуре Haswell — на 56.

На следующем этапе микрооперации по четыре штуки за такт поступают в буфер переупорядочения (ReOrder Buffer), где происходит переупорядочение микроопераций не в порядке их поступления (Out-of-Order), с тем чтобы впоследствии можно было реализовать их более эффективное выполнение на исполнительных блоках.

Отметим, что буфер переупорядочения (ReOrder Buffer) и блок отставки (Retirement Unit) совмещены в едином блоке процессора, но первоначально производится переупорядочение инструкций, а блок Retirement Unit включается в работу позже, когда надо выдать исполненные инструкции в заданном программой порядке. В микроархитектуре Ivy Bridge размер буфера переупорядочения рассчитан на 168 микроопераций, а в микроархитектуре Haswell — на 192 микрооперации.

В микроархитектуре Nehalem в свое время был увеличен размер буфера переупорядочения (ReOrder Buffer, ROB) в сравнении с размером буфера переупорядочения в микроархитектуре Intel Core. Так, если в Intel Core он был рассчитан на 98 микроопераций, то в Nehalem можно было размещать уже 128 микроопераций.

Далее происходит распределение микроопераций по исполнительным блокам. В блоке процессора Unified Scheduler (другое название Reservation Station) формируются очереди микроопераций, в результате чего микрооперации попадают на один из портов функциональных устройств (Dispatch ports). Этот процесс называется диспетчеризацией (Dispatch), а сами порты выполняют функцию шлюза к функциональным устройствам.

В микроархитектурах Ivy Bridge и Haswell кластеры внеочередного выполнения команд (Out-of-Order Cluster) используют так называемые физические регистровые файлы (Physical Register File, PRF), в которых хранятся операнды микроопераций.

Напомним, что в макроархитектуре Nehalem физические регистровые файлы не применялись и каждая микрооперация имела копию операнда или операндов, которые ей требуются. Фактически это означало, что блоки кластера внеочередного выполнения команд должны были иметь достаточно большой размер, чтобы иметь возможность вмещать микрооперации вместе с требуемыми им операндами.

Использование PRF позволяет самим микрооперациям сохранять лишь указатели на операнды, но не сами операнды. С одной стороны, такой подход обеспечивает снижение энергопотребления процессора, поскольку перемещение по конвейеру микроопераций вместе с их операндами требует существенных затрат по энергопотреблению. С другой — применение физического регистрового файла позволяет сэкономить размер кристалла, а высвободившееся пространство использовать для увеличения размеров буферов кластера внеочередного выполнения команд.

В микроархитектуре Ivy Bridge физический регистровый файл для целочисленных операндов (PRF Integer) рассчитан на 160 записей, а для операндов с плавающей запятой (PRF Float Point) — на 144 записи.

В микроархитектуре Haswell физические регистровые файлы PRF Integer и PRF Float Point рассчитаны на 168 записей (см. таблицу).

Размер буфера Unified Scheduler, в котором формируются очереди микроопераций к портам функциональных устройств, также изменился в микроархитектуре Haswell. Если в Ivy Bridge он был рассчитан на 54 микрооперации, то в Haswell — на 60.

Если говорить об исполнительных блоках ядра процессора, то в микроархитектуре Ivy Bridge насчитывается шесть портов функциональных устройств (три вычислительных и три для работы с памятью). При этом три вычислительных устройства позволяют проводить восемь операций с данными FP (Float Point) или две операции с 256-битными AVX-данными за такт.

Из трех портов для работы с памятью два являются универсальными и могут реализовывать загрузку данных (Load) или сохранять адрес (Store address). Третий порт предназначен для хранения данных (Store data). Соответственно пропускная способность взаимодействия с кэшем данных L1 составляет 48 байт за такт (два запроса на чтение по 16 байт и один запрос на запись до 16 байт данных).

В микроархитектуре Haswell количество портов функциональных устройств увеличено до восьми. К тому, что было в микроархитектуре Ivy Bridge, добавили еще один порт для хранения адреса (Store address) и вычислительный порт для операций с целыми числами и операций сдвига (Integer ALU & Shift). Таким образом, процессоры Haswell, по сравнению с процессором Ivy Bridge, могут одновременно (за один такт процессора) выполнять больше операций.

Если говорить о других изменениях в микроархитектуре Haswell, то необходимо отметить, что изменилась пропускная способность (но не размер) кэшей L1 и L2. Так, если в Ivy Bridge для кэша данных L1D скорость чтения (Load bandwidth) составляла 32 байт за цикл, то в микроархитектуре Haswell — уже 64 байт. Аналогично, в Ivy Bridge для кэша данных L1D скорость записи (Store bandwidth) составляла 16 байт за цикл, а в микроархитектуре Haswell — уже 32 байта за цикл.

Кроме того, если в Ivy Bridge пропускная способность между кэшем L2 и L1 составляла 32 байта за цикл, то в микроархитектуре Haswell она равна 64 байта за цикл.

Также немного изменен TLB-буфер кэша L2.

Напомним, что буфер TLB (Translation Look-aside Buffers) — это специальный кэш процессора, в котором сохраняются адреса декодированных инструкций и данных, что позволяет значительно сократить время доступа к ним. Этот кэш предназначен для сокращения времени преобразования виртуального адреса данных или инструкций в физический. Дело в том, что процессор использует виртуальную адресацию, а для доступа к данным в кэше или оперативной памяти нужны реальные физические адреса. Преобразование виртуального адреса в физический занимает приблизительно три такта процессора. TLB-кэш хранит результаты предыдущих преобразований, благодаря чему преобразование адреса данных, применявшихся ранее, возможно осуществлять за один такт.

В процессорах Intel c микроархитектурой Haswell и Ivy Bridge (как и в процессорах Intel на базе других микроархитектур) используется двухуровневый кэш TLD (и L2 TLB), причем если кэш L2 TLB является унифицированным, то L1 TLB-кэш разделен на буфер данных и буфер инструкций. Нужно отметить, что L1 TLB-кэши инструкций и данных в микроархитектуре Haswell не претерпели изменений — они точно такие же, как и в микроархитектуре Ivy Bridge. L1 TLB-кэш инструкций является 4-канальным и поддерживает страницы емкостью как 4 К (128 страниц), так и 2 М/4 M (восемь страниц на поток инструкций).

L1 TLB-кэш данных также 4-канальный и поддерживает страницы емкостью 4 К (64 страницы), 2 М/4 M (32 страницы) и 1 G (4 страницы).

L2 TLB кэш в микроархитектуре Ivy Bridge рассчитан на 512 страниц 4 К и является 4-канальным. В микроархитектуре Haswell этот кэш является 8-канальным и рассчитан на 1024 страницы 4 K и 2 М.

Есть и еще одно нововведение, которое заключается в том, что процессоры Haswell будут поддерживать расширенный набор инструкций Intel AVX2 (Advanced Vector Instructions).

Рассмотренные нами изменения в микроархитектуре Haswell в конечном счете позволяют процессору выполнять больше инструкций за один такт в сравнении с процессором Ivy Bridge, то есть эти изменения отражаются на росте производительности процессора.

Однако, как мы уже отмечали, философия процессоров Intel четвертого поколения заключается не только в производительности, но и в низком энергопотреблении, и в масштабируемости.

Что касается низкого энергопотребления, то, похоже, Intel удалось сделать невозможное: при производительности выше чем у процессора Ivy Bridge энергопотребление процессора Haswell в несколько раз ниже!

Достигнуто это за счет того, что в системах на базе процессора Haswell используются новые состояния энергопотребления S0ix, которые позаимствованы у процессоров Intel Atom (такие режимы энергопотребления были реализованы еще в процессорах Moorestown).

Напомним, что традиционно система может находиться либо в активном состоянии S0 (обычный рабочий режим), либо в одном из четырех состояний «сна» S1-S4.

В состоянии S1 все процессорные кэши сброшены и процессор прекратил выполнение инструкций. Однако поддерживается питание процессора и оперативной памяти, а устройства, которые не обозначены, что должны оставаться включенными, могут быть отключены. Состояние S2 — это еще более глубокое состояние «сна», когда процессор отключен.

Состояние S3 (другое название — Suspend to RAM (STR), или «ждущий» режим («Standby»)) — это состояние, в котором на оперативную память (ОЗУ) продолжает подаваться питание и она остается практически единственным компонентом, потребляющим энергию.

Состояние S4 известно как гибернация (Hibernation). В этом состоянии всё содержимое оперативной памяти сохраняется в энергонезависимой памяти (например, на жестком диске или SSD).

Состояния S0ix (S0i1, S0i2, S0i3, S0i4) аналогичны состояниям S1, S2, S3 и S4 в смысле энергопотребления, но отличаются от них тем, что для перехода системы в активное состояние S0 требуется гораздо меньше времени. К примеру, для перехода из состояния S0 в состояние S0i3 требуется 450 мкс, я для обратного перехода — 3,1 мс.

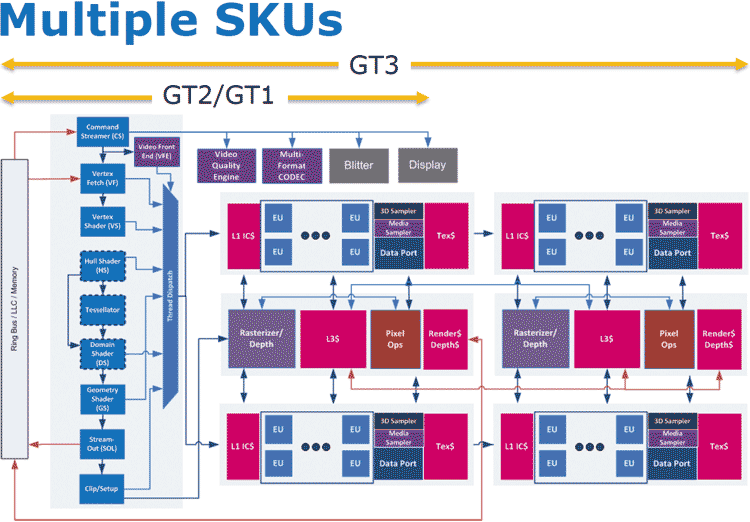

Графическое ядро в микроархитектуре Haswell

Одно из основных нововведений в микроархитектуре Haswell — это новое графическое ядро c поддержкой DirectX 11.1, OpenCL 1.2 и OpenGL 4.0. Но самой главное, что графическое ядро в микроархитектуре Haswell теперь масштабируемое. Как уже отмечалось, будут существовать варианты ядра GT3, GT2 и GT1.

Ядро GT1 будет иметь минимальную производительность, и этим ядром, предположительно, будут оснащаться только младшие двухъядерные модели процессоров. Настольные четырехъядерные процессоры, по всей видимости, будут оснащаться ядром GT2, а мобильные процессоры — ядрами GT2 и GT3.

Блок-схема графического ядра Haswell

В графическом ядре GT3 появится второй вычислительный блок, за счет чего удвоится количество блоков растеризации, пиксельных конвейеров, вычислительных ядер и сэмплеров. Ожидается, что GT3 будет вдвое производительнее GT2.

Ядро GT3 содержит 40 исполнительных блоков, 160 вычислительных ядер и четыре текстурных блока. Для сравнения напомним, что в графическом ядре Intel HD Graphics 4000 процессоров Ivy Bridge содержится 16 исполнительных устройств, 64 вычислительных ядра и два текстурных блока. Поэтому, несмотря на приблизительно одинаковые тактовые частоты их работы, графическое ядро Intel GT3 вдвое превосходит своего предшественника по уровню производительности в бенчмарке Unigine Heaven.