Первый чип с проектной нормой 65 нанометров

24 ноября прошлого года корпорация Intel объявила об изготовлении первой в мире полнофункциональной микросхемы SRAM (статической оперативной памяти), в которой использован технологический процесс следующего поколения с проектной нормой 65 нанометров, планируемый к внедрению в массовое производство в 2005 году на 300-миллиметровых подложках.

65-нанометровом технологическом процессе Intel (кодовое название — P1264) используются

новые транзисторы, имеющие длину затвора всего 35 нм. Это будут самые маленькие

и при этом самые быстродействующие КМОП-транзисторы, используемые в массовом

производстве. Для сравнения: наиболее совершенные транзисторы, применяемые сегодня

при изготовлении процессора Intel Pentium 4, имеют длину затвора 50 нм. Быстродействующие

транзисторы малых размеров — это основа для быстродействующих процессоров.

65-нанометровом технологическом процессе Intel (кодовое название — P1264) используются

новые транзисторы, имеющие длину затвора всего 35 нм. Это будут самые маленькие

и при этом самые быстродействующие КМОП-транзисторы, используемые в массовом

производстве. Для сравнения: наиболее совершенные транзисторы, применяемые сегодня

при изготовлении процессора Intel Pentium 4, имеют длину затвора 50 нм. Быстродействующие

транзисторы малых размеров — это основа для быстродействующих процессоров.

Корпорация Intel использовала в новом технологическом процессе второе поколение своей технологии высокоэффективного напряженного кремния (Strained Silicon), что позволило повысить рабочие токи транзисторов и их быстродействие при увеличении себестоимости всего на два процента.

Новый процесс также предусматривает применение восьми слоев медных соединений и нового low-k-диэлектрического материала, благодаря чему повышается скорость распространения сигналов в кристалле и снижается энергопотребление процессора.

Переход на 65-нанометровый техпроцесс позволит корпорации Intel удвоить количество транзисторов, размещаемых на одном кристалле, по сравнению с применяемыми сегодня технологиями.

«Это достижение выводит 65-нанометровую технологию корпорации Intel на финишную прямую. Таким образом, мы продолжаем 15-летнюю традицию внедрения раз в два года производственного процесса нового поколения. В действительности же прошло всего 20 месяцев с момента, когда мы сообщили о построении полнофункциональных компонентов SRAM на базе 90-нанометрового процесса, который сегодня внедряется в производство, — заявил доктор Сунлинь Чжоу (Sunlin Chou), старший вице-президент и генеральный менеджер подразделения Intel Technology and Manufacturing Group. — Новый 65-нанометровый техпроцесс позволит нам выпускать более совершенную продукцию с меньшими затратами, внедряя новые технологии и согласуясь с законом Мура».

На базе нового 65-нм технологического процесса корпорация Intel изготовила полнофункциональные компоненты SRAM объемом 4 Мбит с чрезвычайно малым размером ячейки памяти — 0,57 мкм2. Уменьшение размера ячейки SRAM позволяет увеличить объем кэш-памяти и соответственно производительность процессоров. Новые ячейки SRAM имеют хорошие рабочие характеристики и большой запас по соотношению «сигнал/шум», указывающий на прекрасные параметры переключения. Каждая ячейка памяти SRAM содержит шесть транзисторов (рис. 1), 10 млн. которых может поместиться на одном квадратном миллиметре, что по площади примерно сопоставимо с кончиком стержня шариковой ручки.

Рис. 1. Ячейка SRAM-памяти размером 0,57 мкм2, состоящая из шести транзисторов

«Разработка 65-нанометрового технологического процесса корпорации Intel успешно движется вперед, и мы уже производим такие подложки и компоненты на нашем опытном производстве, — заявил Марк Бор (Mark Bohr), старший почетный сотрудник и директор по технологической архитектуре и интеграции корпорации Intel. — К 2005 году мы будем первой компанией, внедрившей 65-нанометровый процесс в массовое производство».

Полупроводниковые компоненты на базе 65-нм техпроцесса были изготовлены на опытном заводе D1D (рис. 2) корпорации Intel по обработке 300-миллиметровых подложек в г.Хиллсборо (шт. Орегон), где этот технологический процесс и был разработан. D1D — самый современный завод корпорации, обладающий самой большой среди производств Intel единой «чистой комнатой» площадью более 16 тыс. м2 — примерно три с половиной футбольных поля.

Рис. 2. Фабрика D1D корпорации Intel в г.Хиллсборо (шт. Орегон)

65-нанометровый технологический процесс интересен не только малыми размерами транзисторов, низким энергопотреблением и новыми технологиями и материалами, но и тем, что впервые в отрасли для производства микросхемы с проектной нормой 65 нм был использован литографический процесс с длиной волны источника 193 нм. Отметим, что сегодняшняя 130-нанометровая технология производства процессоров предусматривает использование литографического процесса с длиной волны источника 248 нм. Впрочем, прежде чем говорить о значимости этого события, давайте вспомним, в чем заключается процесс литографии и почему именно от длины волны источника зависят размеры получаемых транзисторов.

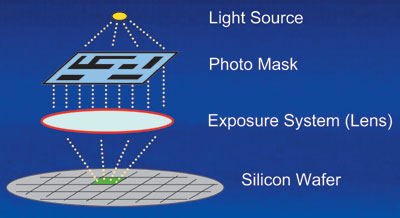

Обычно рисунок будущих приборов и схем делается так. Сначала тем или иным путем изготавливается увеличенное изображение (маска) прибора, которое потом с уменьшением переносится на полупроводниковую пластинку, покрытую фоточувствительным слоем, то есть фотографируется с уменьшением (рис. 3). Дальнейший процесс изготовления прибора весьма сложен и включает много циклов травления и осаждения новых слоев различных материалов, но почти перед каждой операцией требуются нанесение фоточувствительного слоя (резиста) и фотографирование маски с каким-то новым рисунком. Процесс получения рисунка называют литографией, а установки, на которых это делают, — литографами.

Рис. 3. Упрощенная схема литографического процесса

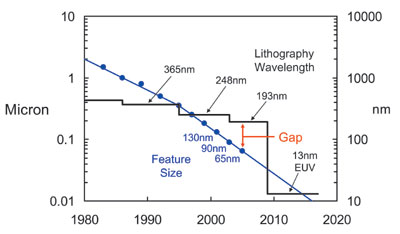

Несмотря на кажущуюся простоту литографического процесса, именно данный этап производства микросхем является наиболее сложным. Для того чтобы транзисторы сделать меньше, необходимо уменьшить геометрические размеры линий, наносимых на слой фоторезиста. Переход ко все более и более малым размерам происходит за счет совершенствования оптических схем и вспомогательных процессов. Но всему есть предел — сфокусировать лазерный луч в точку, оказывается, не так-то просто. Дело в том, что в соответствии с законами волновой оптики минимальный размер пятна, в которое фокусируется лазерный луч (на самом деле это не просто пятно, а дифракционная картина), определяется помимо прочих факторов и длиной волны источника: RES = K1(l/NA), где l — длина волны источника, NA — числовая апертура объектива. Поэтому, когда возможности текущего литографического процесса оказываются исчерпанными, требуется переход на более короткие длины волн. Как правило, события развиваются по следующему сценарию: сначала возникает нужный источник излучения, потом разрабатываются оптика, резисты, установки для экспонирования, а затем начинается промышленное освоение диапазона. Именно это позволяет уменьшать размеры элементов интегральной схемы. С середины 80-х в фотолитографии стало использоваться ультрафиолетовое излучение, получаемое с помощью лазера. Идея проста: длина волны ультрафиолетового излучения меньше, чем длина волны света видимого диапазона, а следовательно, возможно получить и более тонкие линии на поверхности фоторезиста. До недавнего времени для литографии использовалось глубокое ультрафиолетовое излучение (Deep Ultra Violet, DUV) с длиной волны 248 нм (рис. 4). Однако, когда фотолитография перешагнула границу 200 нм, возникли серьезные проблемы, которые впервые за историю этой технологии поставили под сомнение возможность ее дальнейшего использования. Например, при длине волны меньше 200 мкм слишком много света поглощается светочувствительным слоем, поэтому усложняется и замедляется процесс передачи шаблона схемы на процессор. Подобные проблемы побуждают исследователей постоянно совершенствовать литографическую технологию.

Рис. 4. Изменение длины волны источника в литографическом процессе

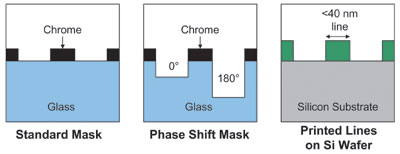

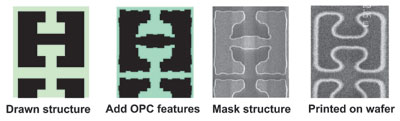

Возвращаясь к технологическому процессу с проектной нормой 65 нм при использовании литографического процесса с длиной волны 193 нм, отметим, что фактически речь идет об адаптации 90-нанометрового технологического процесса (в котором также используется литографический процесс с длиной волны 193 нм) для получения микросхем по 65-нанометровой технологии. Фактически, длина волны 193 нм не подходит для 65-нанометрового технологического процесса, поэтому, чтобы можно было использовать именно эту длину волны, пришлось пойти на ухищрения, дабы обойти законы природы. Речь идет об использовании масок с фазовым сдвигом PSM (Phase Shift Mask), которые позволяют получать линии толщиной менее 40 нм при помощи 193-нанометрового излучения (рис. 5) и масок с оптической коррекцией OPC (Optical Proximity Correction) — рис. 6.

Рис. 5. Маски с фазовым сдвигом PSM

Рис. 6. Маски с оптической коррекцией OPC

Собственная группа корпорации Intel по изготовлению литографических масок сыграла ключевую роль в создании усовершенствованных масок, позволивших применить сегодняшнее литографическое оборудование, работающее на длине волны 193 нм, для 65-нм технологического процесса. Начиная с 2005 года технологический процесс с проектной нормой 65 нм планируется внедрить в массовое производство на заводе D1D и затем перенести на другие заводы, работающие с 300-миллиметровыми подложками.

В статье использованы материалы, предоставленные корпорацией Intel.